I recently wrote about my problems that arose when I re-organized the library of VHDL modules that goes with the XESS FPGA boards, so I thought it would be good to show how the library is now structured.

I recently wrote about my problems that arose when I re-organized the library of VHDL modules that goes with the XESS FPGA boards, so I thought it would be good to show how the library is now structured.

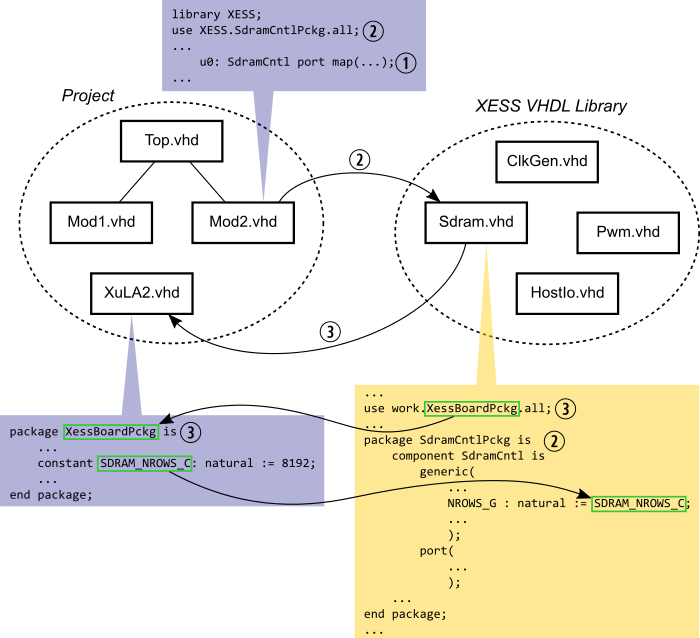

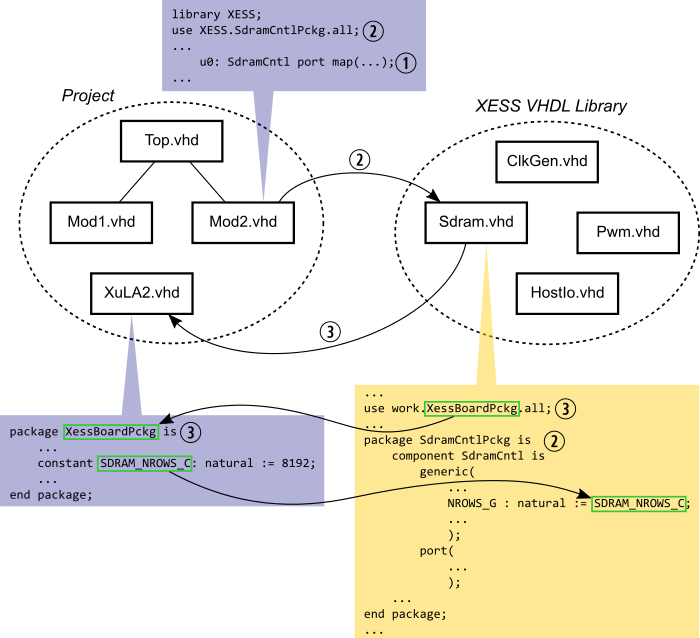

The main problem with my previous library was that I needed two libraries: one for the XuLA board and another, slightly different, library for the XuLA2 board. It was always a problem keeping them in sync because I would fix a problem in one and forget to merge that solution into the other. All this effort was unwarranted since the libraries were nearly identical: the differences between them amounted to some constant definitions and a few places where different versions of Xilinx primitives were used. I could merge the separate libraries into a single unified library by collecting the constants and some conditional component generation flags for each board into its own file and then customize the library for a given project by including the constant/flags file for a particular board. The figure below shows how that's done.

As an example, an FPGA project for the XuLA2 board may include several VHDL files arranged in a hierarchy. One of those files, say Mod2.vhdl, may need to access the SDRAM on the XuLA2 board by instantiating the SdramCntl module (see (1)).

The SdramCntl module is in the SdramCntlPckg package that's in the XESS library (see (2)). The VHDL synthesizer will look in the files of the XESS library and find the SdramCntlPckg package in the Sdram.vhd file.

Within the Sdram.vhd file, the SdramCntl module uses the NROWS_G generic parameter to customize the controller for the number of rows in the SDRAM chip on the XuLA2 board. (There are a number of other generic parameters for the SDRAM as well.) In the old version of the XESS library, the NROWS_G parameter was initialized with the literal constant 8192, which was the number of rows in the SDRAM chip used on the XuLA2 board. Now, however, the NROWS_G parameter is initialized with another constant: SDRAM_NROWS_C. The value for this constant can be found in the XessBoardPckg package. But this package is not stored in the XESS library; instead, it is stored in the work library which is a local library associated with each particular FPGA project (see (3)). In this example, the VHDL synthesizer will find XessBoardPckg in the XuLA2.vhd file in the project directory. Inside, it will find the value for SDRAM_NROWS_C and plug that into the NROWS_G generic parameter.

The advantage of this indirection is that, if this project needed to be retargeted to the FPGA on the XuLA board, then that's easily done by removing the XuLA2.vhd file from the project and adding the XuLA.vhd file containing a different set of constants for the XuLA board.

Also note that the constant from the XuLA2.vhd file is used to initialize the value of the generic parameter, NROWS_G. It is not used directly in the rest of the SdramCntl module. Instead, NROWS_G is used wherever the number of SDRAM rows is needed. This gives the user of the library the flexibility of overriding this value by specifying another value for the generic parameter when instantiating the module.

That pretty much covers the main wrinkle of the new XESS VHDL library. You can check out the details on Github.

Share on Twitter Share on Facebook Share on Reddit

Comments

New Comment