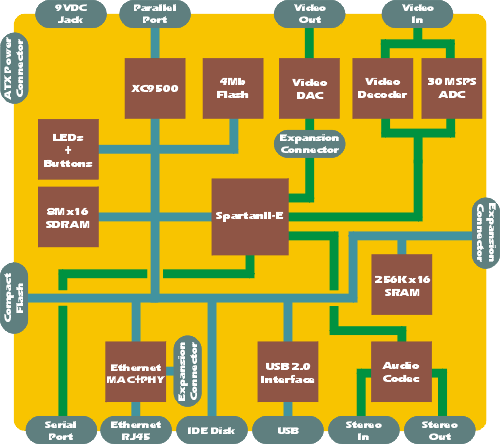

The XSB Board brings you the power of the XILINX Spartan-2E FPGA embedded in a framework for processing

video and audio signals. The XSB-300E Board provides an XC2S300E FPGA with 300,000 gates.

The XSB-300E can accept six channels of PAL, SECAM, or NTSC video with up to 9-bits of

resolution on the red, green, and blue channels and can output video images through a 80 MHz,

30-bit video DAC. The XSB-300E can also process four channels of stereo audio with up to 20 bits

of resolution and a bandwidth of 20 KHz. A 256K x 16 SRAM and an 8M x 16 SDRAM are

provided for local buffering of signals and data. An IDE hard disk or Compact Flash card can be

connected to the XSB-300E for long-term non-volatile storage.

The XSB-300E Board has a variety of interfaces for communicating

with the outside world: parallel and serial ports, USB 2.0 port,

and 10/100 Ethernet PHY layer interface. There are also two

independent expansion ports with a total of 75 general purpose I/O pins connected directly to

the XC2S300E and an additional peripheral expansion port with 18 I/O pins.

You configure the XSB-300E Board through a PC

parallel port or from a bitstream stored in the 4 Mbit Flash RAM. The

Flash RAM can also store data for use by the FPGA after configuration is complete.