© 2001 by X Engineering Software Systems Corp., Apex, North Carolina 27502

All rights reserved. No part of this text may be reproduced, in any form or by any means, without permission in writing from the publisher.

The author and publisher of this text have used their best efforts in preparing this text. These efforts include the development, research, and testing of the theories and programs to determine their effectiveness. The author and publisher make no warranty of any kind, expressed or implied, with regard to these programs or the documentation contained in this text. The author and publisher shall not be liable in any event for incidental or consequential damages in connection with, or arising out of, the furnishing, performance, or use of these programs.

XESS, XS40, and XS95 are trademarks of X Engineering Software Systems Corp. XILINX, Foundation, XC4000, and XC9500 are trademarks of XILINX Corporation. Other product and company names mentioned are trademarks or trade names of their respective companies.

The software described in this text is furnished under a license agreement. The software may be used or copied under terms of the license agreement.

# **Using RAM**

## In this chapter you will learn how to:

- Interface to an external RAM with a programmable device.

- Use the internal RAMs found in the XC4000 FPGAs.

- Create RAM modules using the Core Generator.

## RAM

Eventually you will need to incorporate RAM into one of your designs. While you can build multi-bit registers from the flip-flops in a CPLD or FPGA, it is more efficient to use an external RAM chip or a specialized internal RAM-block when you need to store larger amounts of data.

In this chapter we will build a simple design that reads a set of data bytes from RAM, writes the 2'scomplement of the byte values back into the RAM, sums the complemented data values and then displays the sum on the seven-segment LED. We will do two different versions of this design:

- 1. The first version will store the data values in the external asynchronous, byte-wide RAM found on the XS40 and XS95 Boards.

- 2. The second version will store the data values using the internal synchronous, distributed RAM contained in the XC4000 FPGA on the XS40 Board.

## Using an External Asynchronous RAM

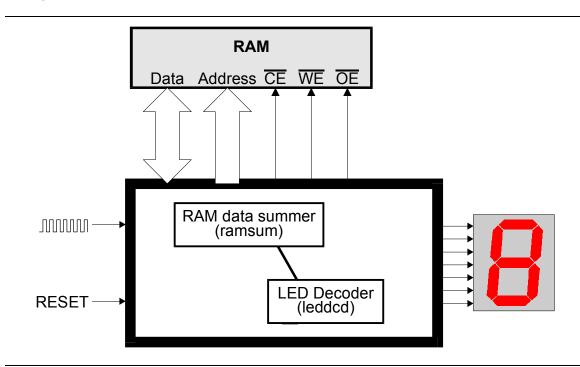

The first version of the RAM summation circuit has the design hierarchy shown in Figure 12. The root module of the design manages the interface to the external asynchronous RAM and sums the data while the lower-level module displays a four-bit hexadecimal value on a seven-segment display.

Figure 12: Design hierarchy for a logic circuit that displays the summation of data in the RAM.

Each of these modules is described by a VHDL file stored in the *dsgn5\_1* project directory that was created as follows.

| New Proje  | ect                 |       | ×                        |

|------------|---------------------|-------|--------------------------|

| Name:      | dsgn5_1             |       | ОК                       |

| Directory: | C:\PRAG21I          |       | Cancel<br><u>B</u> rowse |

| Туре:      | F2.1i               | •     | <u>H</u> elp             |

| Flow:      | C <u>S</u> chematic | ● HDL |                          |

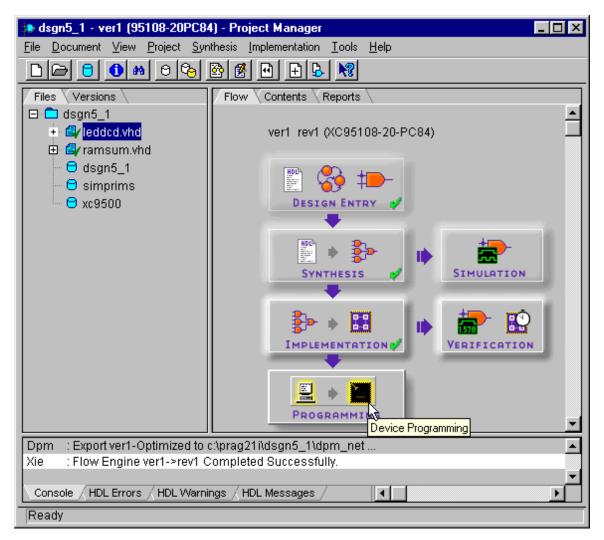

After the VHDL files for the modules were created and added to the project, the **Project Navigator** window appears as follows. Now I will describe the contents of each VHDL file.

| 🐌 dsgn5_1 - 95108-20PC84 - Pro                                                                                      | oject Manager 📃 🗖      | ×        |  |  |  |

|---------------------------------------------------------------------------------------------------------------------|------------------------|----------|--|--|--|

| <u>File D</u> ocument <u>V</u> iew <u>Project</u> <u>Synthesis</u> <u>Implementation</u> <u>T</u> ools <u>H</u> elp |                        |          |  |  |  |

| D 🖻 🖯 🐽 🔿 🕤                                                                                                         | 🖻 🗭 🖻 🖶 💦              |          |  |  |  |

| Files Versions                                                                                                      | Flow Contents Reports  |          |  |  |  |

| ☐ ☐ dsgn5_1 + ⓓ / leddcd.vhd ① 個 / ramsum.vhd ☐ dsgn5_1                                                             | dsgn5_1                |          |  |  |  |

|                                                                                                                     | 📰 😵 🍋                  |          |  |  |  |

|                                                                                                                     | DESIGN ENTRY           |          |  |  |  |

|                                                                                                                     | SYNTHESIS / SIMULATION |          |  |  |  |

|                                                                                                                     |                        |          |  |  |  |

|                                                                                                                     |                        | <b>•</b> |  |  |  |

| Dpm : Done                                                                                                          |                        |          |  |  |  |

| Pcm : Update: c:\prag21i\dsgn5_1\ramsum.vhd (0, 0)                                                                  |                        |          |  |  |  |

| Pcm : Synopsys server initialization                                                                                |                        |          |  |  |  |

| Console / HDL Errors / HDL Warnings / HDL Messages /                                                                |                        |          |  |  |  |

| Ready                                                                                                               |                        |          |  |  |  |

#### The LED Decoder Module

This LED decoder circuit is almost identical to the one in Chapter 3 except for the addition of a blanking input signal that causes all the LED segments to turn off. This signal will be used to blank the display to separate the digits when displaying a multi-digit hexadecimal number.

The VHDL code for the LED decoder is shown in Listing 4. This code is stored in the leddcd.vhd file in the *dsgn5\_1* project directory.

```

Listing 4: VHDL code for the seven-segment LED decoder module.

```

```

1

library IEEE;

2

use IEEE.std logic 1164.all;

3

use IEEE.numeric std.all;

4

5

package leddcd pckg is

6

7

component leddcd

8

port (

9

blank: in STD LOGIC; -- active-high blanking input

10

: in UNSIGNED (3 downto 0);

d

```

```

11

: out STD LOGIC VECTOR (6 downto 0)

S

12

);

13

end component;

14

15

end leddcd pckq;

16

17

18

library IEEE;

19

use IEEE.std logic 1164.all;

20

use IEEE.numeric std.all;

21

22

entity leddcd is

23

port (

24

blank: in STD LOGIC; -- active-high blanking input

25

d : in UNSIGNED (3 downto 0);

26

: out STD LOGIC VECTOR (6 downto 0)

S

27

);

28

end leddcd;

29

30

architecture leddcd arch of leddcd is

31

signal s tmp: STD LOGIC VECTOR(6 downto 0);

32

begin

33

with d select

34

s tmp <= "1110111" when "0000", -- 0

35

"0010010" when "0001", -- 1

36

"1011101" when "0010", -- 2

37

"1011011" when "0011", -- 3

38

"0111010" when "0100", -- 4

39

"1101011" when "0101", -- 5

40

"1101111" when "0110", -- 6

41

"1010010" when "0111", -- 7

42

"11111111" when "1000", -- 8

43

"1111011" when "1001", -- 9

44

"1111110" when "1010", -- A

45

"0101111" when "1011", -- b

46

"1100101" when "1100", -- C

47

"0011111" when "1101", -- d

48

"1101101" when "1110", -- E

49

"1101100" when others; -- F

50

51

-- zero the outputs if the blanking signal is high,

52

-- otherwise output the LED digit bit pattern

53

s \leq "0000000" when blank='1' else s tmp;

54

end leddcd arch;

```

#### The Root Module

The root module sequences through three main phases:

**Phase 1:** Starting from an upper address of RAM and proceeding to address zero, the value stored at each RAM address is read and the two's-complement is computed and written back to the same address.

- **Phase 2:** Restarting from the upper address and proceeding to address zero, each value is read from RAM and added to a sum register.

- **Phase 3:** The sum is displayed on the seven-segment LED by blanking the LED segments for a long interval to signal the start of the sum, then the hexadecimal digit for the upper four bits of the sum are displayed, then the LEDs are blanked for a shorter interval and then the hexadecimal digit for the lower four bits is displayed. Then this four-step display process repeats.

The VHDL code for the root module is in the ramsum.vhd (Listing 5). Some highlights from the code are given below.

- Line 4: The root module accesses the component declaration for the LED decoder by using the leddcd\_pckg package that is part of the WORK library. The WORK library is an *implicit library* that has every project module as a member. We could have explicitly created a library and added the leddcd.vhd file to it as we did in Chapter 3, but using the WORK library is a bit simpler.

- Lines 6–17: The interface to the design is declared here. The reset and clock inputs drive the actions of the state machine that controls the operation of the circuit. Data is passed to and from the RAM using the address and data buses along with the chip-enable, write-enable and output-enable control signals. (Note that the RAM data bus is declared as an inout since the same signals are used to get data from the RAM as to send data to it.)

- Lines 20–21: The four-bit RAM address register is declared on these lines as well as the constant for the address of the upper end of the RAM data that will be summed. For this example, the circuit will complement and sum eleven bytes of data from address zero to ten, inclusive.

- Lines 22–23: Two registers that are the same width as the RAM data bus are declared here. One register holds the current value read from the RAM while the other holds the sum of the RAM data values.

- Lines 24–27: These lines declare a time delay register and the constants for the time intervals involved with the display of the hexadecimal digits in the sum.

- Lines 28–29: These lines declare a four-bit bus for sending the hexadecimal digit to the LED decoder and a control signal to force the LED display to blank.

- Lines 31–33: The nine states of the state machine are declared along with a register that holds the current state.

- Line 37: This is the start of the process that computes the next state for the state machine given the current state, RAM address and delay timer value. The values for the RAM address, data and control signals are also generated in this process.

- Lines 40–50: The default outputs for this process are defined here. The state, RAM address, summation and RAM byte registers all retain their current values unless explicitly changed within the process body. The delay register is decremented. The LED display is blanked. The RAM is enabled, but any

read or write operations are disabled. The data bus is tristated to remove any chance of contention between the FPGA or CPLD and the RAM.

- Line 52: This is the start of the case statement that computes the outputs from this process based on the current state stored in the st r register.

- Lines 53–55: The init state initializes the state machine for the start of the loop that complements the contents of RAM. The address register is set to point to the upper bound of the RAM data range and the state machine is moved to the start of the two's-complement loop (invertr).

- Lines 56–59: The invertr state activates the outputs of the external RAM. The FPGA or CPLD will tristate its own outputs to the RAM data bus so that there is no contention (the default statement handles this). The value from RAM is complemented and stored in the RAM byte register. Then the state machine is moved to the state where the complemented data is written back to the RAM (invertw).

- Lines 60–63: The invertw state activates the write-enable of the external RAM during the second half of the clock cycle (when the clock is low). The value in the RAM byte register is sent out to the RAM on the data bus. Then the state machine is moved to a NOP state to terminate the RAM write (invertnop).

- Lines 64–74: The invertnop state keeps the RAM address stable while the writeenable returns to its quiescent state (the default operation statements handle this). The value in the RAM byte register remains on the output bus to the RAM for the same reason. If the current RAM address is zero indicating the complementation loop is finished, then the RAM address is reloaded with the starting address of the (now complemented) RAM data. Then the state machine is moved to the start of the summation loop (add). If not all the RAM data has been complemented yet, then the RAM address is decremented and the state machine returns to the start of the complementation loop (invertr).

- Lines 75–85: The add state activates the outputs of the external RAM. The value from RAM is added to the summation register. If the current RAM address is zero indicating the summation loop is finished, then the time delay register is loaded with the initial blanking interval for the LED display. Then the state machine is moved to the start of the display loop (display\_blank). If all the RAM data has not been summed, then the RAM address is decremented and the state machine stays in the add state.

- Lines 86–91: The display\_blank state blanks the LED display and decrements the delay timer (the default operation statements handle this). Once the delay timer reaches zero, it is reloaded with the time interval for display of a digit and the state machine is moved into the display upper digit state.

- Lines 92–99: The display\_upper\_digit state unblanks the LED display and sends the upper four bits of the sum to the LED decoder. The delay timer is also decremented. Once the delay timer reaches zero, it is reloaded with the time interval for blanking the display between digits and then the state machine is moved into the display interdigit state.

- Lines 100–105: The display\_interdigit state blanks the LED display and decrements the delay timer (the default operation statements handle this). Once the delay timer reaches zero, it is reloaded with the time interval for display of a digit and the state machine is moved into the display\_lower\_digit state.

- Lines 106–113: The display\_lower\_digit state unblanks the LED display and sends the lower four bits of the sum to the LED decoder. The delay timer is also decremented. Once the delay timer reaches zero, it is reloaded with the time interval for blanking the display before the sum is displayed and then the state machine is moved into the display\_blank state.

- Lines 120–134: This process updates the state, address, data, sum and time delay registers with their new values on the rising edge of the clock. The reset input synchronously clears the sum register and transfers the state machine into its starting state.

- Line 136: The four-bit RAM address is padded with leading zeroes to form the complete address passed to the external RAM.

- Line 137: The LED decoder is passed the blanking signal and the four-bit hexadecimal code for the digit to be displayed. The outputs of the LED decoder drive the seven-segment LEDs.

```

Listing 5: VHDL code for the root module.

```

```

1

library IEEE;

2

use IEEE.std logic 1164.all;

3

use IEEE.numeric std.all;

4

use WORK.leddcd pckg.all;

5

6

entity ramsum is

7

port (

8

rst : in STD LOGIC;

-- reset

9

-- clock

clk : in STD LOGIC;

: out UNSIGNED(16 downto 0);

10

-- RAM address bus

а

: inout UNSIGNED(7 downto 0);

11

d

-- RAM data bus

ce_n : out STD_LOGIC;-- RAM chip-enablewe_n : out STD_LOGIC;-- RAM write-enableoe_n : out STD_LOGIC;-- RAM output-enable

12

13

14

15

s : out STD LOGIC VECTOR(6 downto 0) -- outputs to LED segments

16

);

17

end ramsum;

18

19

architecture ramsum arch of ramsum is

20

signal addr r, next addr: UNSIGNED(3 downto 0); -- address register

21

constant maxaddr : UNSIGNED := TO UNSIGNED(10,addr r'length); -- upper address

22

signal b r, next b : UNSIGNED(d'length-1 downto 0); -- stores byte from RAM

23

signal sum r, next sum : UNSIGNED(d'length-1 downto 0); -- stores sum of RAM bytes

24

signal delay r, next delay : UNSIGNED(22 downto 0); -- delay counter

25

constant blank dly : UNSIGNED := TO UNSIGNED(5 000 000,delay r'length);

26

constant interdigit dly : UNSIGNED := TO UNSIGNED(1 600 000,delay r'length);

27

constant digit dly : UNSIGNED := TO UNSIGNED(2 500 000,delay r'length);

28

signal digit : UNSIGNED(3 downto 0); -- LED hex digit to display

signal blank : STD_LOGIC; -- LED digit blanking signal

29

30

-- states for the state machine

31

type state is (init, invertr, invertw, invertnop, add, display blank,

344

© 2001 by XESS Corp.

```

```

32

display upper digit, display interdigit, display lower digit);

33

signal st_r, next_st : state; -- state register

34

begin

35

36

-- this process computes the actions of the state machine in each state

37

process(clk,st r,addr r,sum r,b r,delay r,d)

38

begin

39

-- default outputs unless otherwise specified

40

next st <= st r;-- next state is the same as the current state

41

next addr <= addr r; -- don't change the RAM address</pre>

42

next sum <= sum r; -- don't update the sum register</pre>

43

next b <= b r; -- don't reload the RAM byte register

44

next delay <= delay r-1; -- decrement the delay counter

45

digit <= TO UNSIGNED(0,digit'length); -- output a '0' LED digit</pre>

46

blank <= '1'; -- blank the LED display

47

ce n <= '0'; -- enable the RAM

48

we n <= '1'; -- don't write to the RAM

49

oe n <= '1'; -- don't read from the RAM

50

<= (others=>'Z'); -- tristate the but to the RAM

d

51

52

case st r is -- case statement for the state machine

53

when init => -- initialization state

54

next_addr <= maxaddr; -- start inverting from the upper address</pre>

55

next st <= invertr; -- enter the RAM inversion loop</pre>

56

when invertr => -- read the contents of the RAM location

57

oe n <= '0'; -- enable the RAM outputs

58

next b <= TO_UNSIGNED(0,next_b'length) - d; -- invert byte from RAM</pre>

59

next st <= invertw; -- go to RAM-write state</pre>

60

when invertw => -- write inverted byte value into same RAM location

61

we_n <= clk; -- write RAM in 2nd half of clock cycle

d <= b_r; -- output inverted byte value to RAM</pre>

62

63

next st <= invertnop; -- go to RAM no-op state</pre>

64

when invertnop => -- terminate RAM-write cleanly

65

d <= b r; -- maintain output of inverted byte value to RAM

66

if addr r = TO UNSIGNED(0, addr r'length) then

67

-- reached the lower address of the RAM data

68

next addr <= maxaddr; -- reload register with upper address</pre>

69

next st <= add; -- enter the summation loop</pre>

70

else

71

-- haven't inverted all the RAM data yet

72

next addr <= addr r - 1;-- address the next RAM location</pre>

73

next st <= invertr; -- return to beginning of the inversion loop

74

end if;

75

-- sum the inverted data from RAM

when add =>

76

oe_n <= '0'; -- enable the RAM outputs</pre>

77

next_sum <= sum_r + d; -- add the RAM data to the sum</pre>

78

if addr r = TO UNSIGNED(0, addr r'length) then

79

-- reached the lower address of the RAM data

80

next delay <= blank dly;-- load display interval counter</pre>

81

next_st <= display_blank; -- now display the sum</pre>

82

else

83

-- haven't summed all the RAM data yet so stay in this state

84

next_addr <= addr_r - 1;-- address the next RAM location</pre>

85

end if;

86

when display blank => -- blank the display

87

if delay r = TO UNSIGNED(0, delay r'length) then

88

-- initial display blanking is complete

89

next delay <= digit dly; -- load digit display interval</pre>

90

next st <= display upper digit; -- now display the upper sum digit

```

```

91

end if;

92

when display upper digit => -- display the upper digit of the sum

93

blank <= '0';</pre>

-- activate the LED

94

digit <= sum r(7 downto 4); -- display the upper 4-bits of the sum

95

if delay r = TO UNSIGNED(0, delay r'length) then

96

-- upper digit display is complete

97

next delay <= interdigit dly; -- load inter-digit blanking interval

98

next st <= display interdigit; -- blank the display between digits

99

end if;

100

when display interdigit => -- blank the display between sum digits

101

if delay r = TO UNSIGNED(0, delay r'length) then

102

-- inter-digit display blanking is complete

103

next delay <= digit dly; -- load digit display interval</pre>

104

next st <= display lower digit; -- now display the lower sum digit

105

end if;

106

when display lower digit => -- display the lower digit of the sum

107

blank <= '0';

-- activate the LED

108

digit <= sum_r(3 downto 0); -- display the lower 4-bits of the sum</pre>

109

if delay r = TO UNSIGNED(0, delay r'length) then

110

-- lower digit display is complete

111

next delay <= blank dly; -- load blanking interval between loops

112

next st <= display blank; -- loop and display the sum again

113

end if;

114

when others = -- error state

115

next st <= init; -- re-initialize the state machine on an erroneous state

116

end case;

117

end process;

118

119

-- this process updates the registers on every rising clock edge

120

process(clk)

121

begin

122

if clk'event and clk='1' then -- trigger on rising clock edge

123

if rst='1' then -- synchronous reset

124

st r <= init;</pre>

125

sum r <= TO UNSIGNED(0, sum r'length);</pre>

126

else -- update the registers

127

st r <= next st;

128

sum r <= next sum;

129

addr_r <= next_addr;

130

b r <= next b;

131

delay r <= next delay;</pre>

132

end if;

133

end if;

134

end process;

135

136

a <= "00000000000" & addr r;

137

u1: leddcd port map(blank=>blank, d=>digit, s=>s);

138

139

end ramsum arch;

```

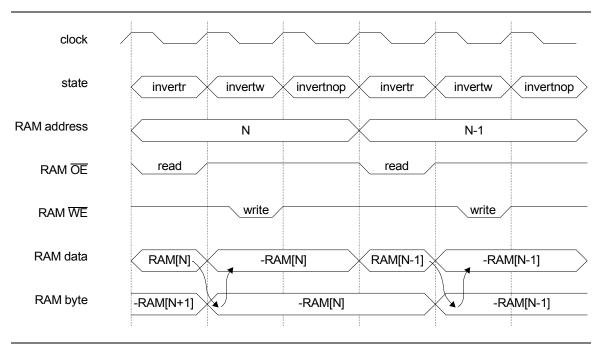

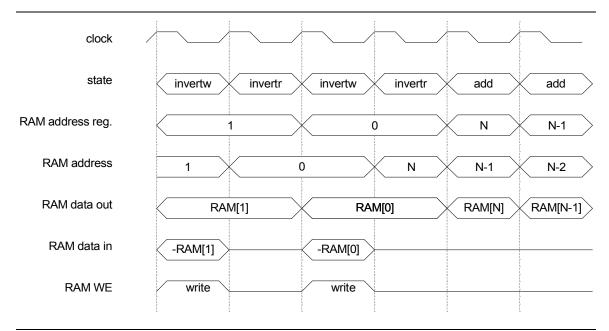

Figure 13 shows the waveforms for the phase when the RAM data is complemented. RAM address N is output at the start of the invertr clock cycle and the RAM outputenable is activated. The data stored at address N is output by the RAM to the FPGA or CPLD where it is complemented and stored into the RAM byte register at the start of the invertw cycle. The complemented value in the byte register is sent back to the RAM and the RAM write-enable is pulsed low during the second half of the invertw cycle, thus writing the complemented data back to address N. The RAM address and data are

held stable during the following invertnop cycle and then the entire operation is repeated for RAM address N-1.

#### Figure 13: Timing waveforms for the asynchronous RAM summation circuit.

The timing waveforms illustrate the fundamental principles involved when writing to an asynchronous RAM:

- 1. The address to the RAM must be held stable during the entire time the writeenable is active-low. Otherwise, data may be erroneously written to some other address instead of, or in addition to, the desired address. That's because write operations to an asynchronous RAM occur as long as the write-enable is low, not just on an edge transition.

- 2. The data to the RAM must be held stable at the rising edge of the write-enable pulse. Otherwise, an incorrect data value may be written to the RAM address.

For our design, note that the RAM address is stable for an entire cycle both before and after the write-enable pulse, and the RAM data is stable for an entire cycle before and after the rising edge of the write-enable pulse. This allows a large setup time for the address and data before the write-enable pulse, and provides a large hold time after the pulse.

### Synthesizing and Implementing the Design

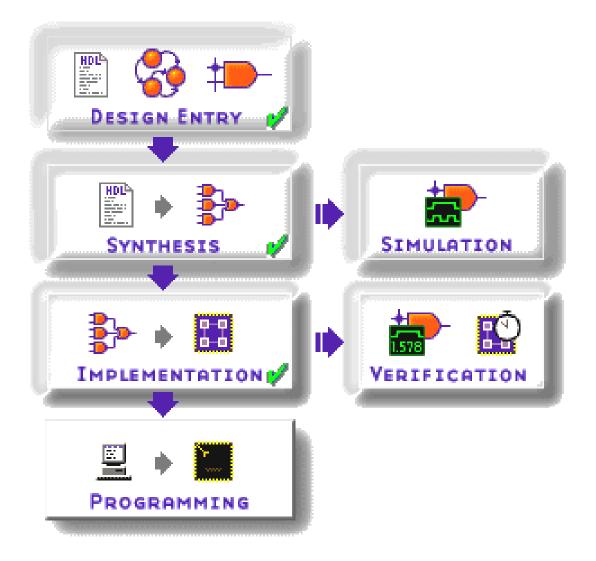

Once the modules are checked for syntax and any errors are removed, we can run the synthesis and implementation tools to create the configuration bitstream for the FPGA or CPLD. Click on the Implementation icon to run the synthesizer and the implementation tools sequentially.

| 🐌 dsgn5_1 - 95108-20PC84 - Pro                                                                                      | iject Manager                         | . 🗆 🗵    |  |  |  |

|---------------------------------------------------------------------------------------------------------------------|---------------------------------------|----------|--|--|--|

| <u>File D</u> ocument <u>V</u> iew <u>Project</u> <u>Synthesis</u> <u>Implementation</u> <u>T</u> ools <u>H</u> elp |                                       |          |  |  |  |

| <u> </u>                                                                                                            |                                       |          |  |  |  |

| Files Versions                                                                                                      | Flow Contents Reports                 |          |  |  |  |

| □· □ dsgn5_1 +· ⓐ/ leddcd.vhd ⊡· ⓐ/ ramsum.vhd                                                                      | dsgn5_1                               |          |  |  |  |

| - 🖯 dsgn5_1                                                                                                         | DESIGN ENTRY                          |          |  |  |  |

|                                                                                                                     | · · · · · · · · · · · · · · · · · · · |          |  |  |  |

|                                                                                                                     | SYNTHESIS ?                           |          |  |  |  |

|                                                                                                                     |                                       |          |  |  |  |

|                                                                                                                     |                                       | -        |  |  |  |

| Dpm : Done                                                                                                          | 1)romoum uhd (0, 0)                   | <b>_</b> |  |  |  |

| Pcm : Update: c:\prag21i\dsgn5<br>Pcm : Synopsys server initializa                                                  |                                       | Ŧ        |  |  |  |

| Console / HDL Errors / HDL Warnings / HDL Messages /                                                                |                                       |          |  |  |  |

| Ready                                                                                                               |                                       |          |  |  |  |

We will target this design to the XS95 Board, so set the target device to be an XC95108PC84 with a -20 speed grade. Then select the **ramsum** module as the top-level module for the design.

| Synthesis/Implementation se                                                                      | ettings        | ×                                   |  |  |  |  |

|--------------------------------------------------------------------------------------------------|----------------|-------------------------------------|--|--|--|--|

| Top level: ramsum<br>Version name: leddcd<br>ramsum<br>Synthesis Settings:                       | ▼<br>SET       | <u>R</u> un<br>OK<br><u>C</u> ancel |  |  |  |  |

| - Target Device                                                                                  |                | <u>H</u> elp                        |  |  |  |  |

| Family: XC9500                                                                                   | -              |                                     |  |  |  |  |

| Device: 95108PC84                                                                                | Speed:         | -20 💌                               |  |  |  |  |

| Edit Synthesis/Implementation constraints                                                        |                |                                     |  |  |  |  |

| View Estimated Performance                                                                       | after Optimiza | tion                                |  |  |  |  |

| Auto Run Implementation to<br>Physical Implementation settin<br>Revision name:<br>Control Files: |                | <u>Options</u>                      |  |  |  |  |

Next, we need to set the options for the implementation tools.

| Synthesis/Imp    | lementatio   | n settin  | gs        | ×              |

|------------------|--------------|-----------|-----------|----------------|

| Top level:       | ramsum       |           | -         | <u>R</u> un    |

| Version name:    | ver1         |           |           | OK             |

| Synthesis Settin | igs:         |           | SET       | <u>C</u> ancel |

|                  |              |           |           | <u>H</u> elp   |

| – Target Device  | э            |           |           |                |

| Family: XC9      | 500          | •         |           |                |

| Device: 951      | 08PC84       | -         | Speed:    | -20 💌          |

| Edit Synthes     | is/Implemen  | tation co | nstraints |                |

| 🔲 View Estimat   | ted Performa | nce afte  | r Optimiz | ation          |

| 🗹 Auto Run I     | mplementati  | on tools  |           |                |

| Physical Imple   | ementation s | ettings — |           |                |

| Revis            | ion name:    | rev1      |           | <u>Options</u> |

| Contr            | ol Files:    | SE        | T         | 43             |

Click on the Area button to make the CPLD fitting tool emphasize logic efficiency over operational speed. This option setting is necessary because the design uses a large time delay counter and several comparators that make it difficult to fit into an XC95108 CPLD. Click on the OK button to close the window.

| Op | tions                     |                    |                 |                        | × |

|----|---------------------------|--------------------|-----------------|------------------------|---|

|    | - Implementation Options- |                    |                 |                        |   |

|    | CPLD Optimization Style   | e:                 |                 |                        |   |

|    | Area                      | C <u>B</u> alanced | O <u>S</u> peed | C <u>U</u> ser Defined |   |

|    |                           | Optimize Density   |                 | ✓ Edit Options         |   |

|    | Simulation Options        |                    |                 |                        |   |

|    | Si <u>m</u> ulation:      | Foundation EDIF    |                 | E <u>d</u> it Options  |   |

|    |                           |                    | OK              | Cancel <u>H</u> elp    |   |

Next, click on the SET button so we can specify the constraint file that lists the pin assignments for the XS95 Board.

| Synthesis/Implementation settings             | ×              |  |  |  |  |

|-----------------------------------------------|----------------|--|--|--|--|

| Top level: ramsum                             | <u>R</u> un    |  |  |  |  |

| Version name: ver1                            | ОК             |  |  |  |  |

| Synthesis Settings: SET                       | <u>C</u> ancel |  |  |  |  |

|                                               | <u>H</u> elp   |  |  |  |  |

| Target Device                                 |                |  |  |  |  |

| Family: XC9500                                |                |  |  |  |  |

| Device: 95108PC84 Speed:                      | -20 💌          |  |  |  |  |

| Edit Synthesis/Implementation constraints     |                |  |  |  |  |

| View Estimated Performance after Optimization |                |  |  |  |  |

| Auto Run Implementation tools                 |                |  |  |  |  |

| Physical Implementation settings              |                |  |  |  |  |

| Revision name: rev1                           | <u>Options</u> |  |  |  |  |

| Control Files: SET                            |                |  |  |  |  |

| Settings D                                      | × |

|-------------------------------------------------|---|

| Synthesis Settings Implementation control files | 1 |

| Current Revision Control File Settings:         |   |

| Use Constraints file from: None                 |   |

| Copy Guide file from:                           |   |

| Copy Floorplan files from: None                 |   |

| Current Revision Control file use:              |   |

| Enable Guided MAP and PAR                       |   |

| Enable Floorplanning                            |   |

|                                                 |   |

|                                                 |   |

| OK Cancel <u>H</u> elp                          |   |

Select the Custom entry in the drop-down list of constraint files.

The **Custom** window should appear with the dsgn5\_1.ucf file already in the Constraints File field. If not, click on the Browse button, find this file in the top-level directory of the **dsgn5\_1** project and select it. Then click on the OK button.

| Custom                        | ×      |

|-------------------------------|--------|

| Constraints File: dsgn5_1.ucf | Browse |

| <u> </u>                      | Help   |

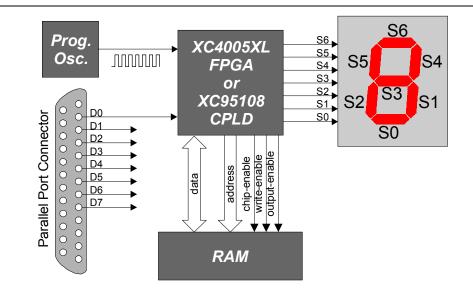

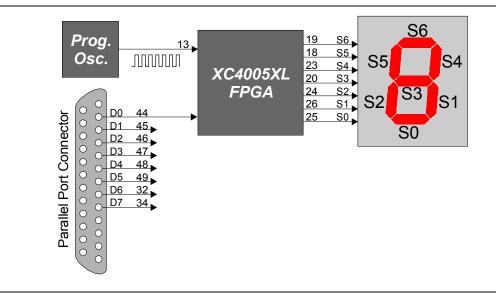

The dsgn5\_1.ucf file should specify the assignments for the FPGA or CPLD pins that connect to the clock, reset, seven-segment LED and RAM address, data and control pins as shown in Figure 14. The pin assignments for the XS95 Board (which is our target for this example) are shown in Listing 6. The equivalent pin assignments for the XS40 Board are given in Listing 7.

Figure 14: Connection of the external RAM, programmable oscillator, parallel port, and LED digit to the pins of the FPGA or CPLD on the XS40 or XS95 Board.

#### Listing 6: Pin assignments for the XS95 Board.

| <pre># pin assignemnts for the XS95 Board</pre>                       |  |

|-----------------------------------------------------------------------|--|

| <pre>net clk loc=p9; # clock from programmable osc.</pre>             |  |

| <pre>net rst loc=p46; # reset from data pin D0 of parallel port</pre> |  |

| net d<0> loc=p44; # RAM data pin D0                                   |  |

| net d<1> loc=p43; # RAM data pin D1                                   |  |

| net d<2> loc=p41; # RAM data pin D2                                   |  |

| net d<3> loc=p40; # RAM data pin D3                                   |  |

| net d<4> loc=p39; # RAM data pin D4                                   |  |

| net d<5> loc=p37; # RAM data pin D5                                   |  |

| net d<6> loc=p36; # RAM data pin D6                                   |  |

| net d<7> loc=p35; # RAM data pin D7                                   |  |

| net a<0> loc=p75; # RAM address pin A0                                |  |

| net a<1> loc=p79; # RAM address pin A1                                |  |

| net a<2> loc=p82; # RAM address pin A2                                |  |

| net a<3> loc=p84; # RAM address pin A3                                |  |

| net a<4> loc=p1;  # RAM address pin A4                                |  |

| net a<5> loc=p3; # RAM address pin A5                                 |  |

| net a<6> loc=p83; # RAM address pin A6                                |  |

| net a<7> loc=p2; # RAM address pin A7                                 |  |

| net a<8> loc=p58; # RAM address pin A8                                |  |

| net a<9> loc=p56; # RAM address pin A9                                |  |

| net a<10> loc=p54;  # RAM address pin A10                             |  |

| net a<11> loc=p55;  # RAM address pin A11                             |  |

| net a<12> loc=p53;  # RAM address pin A12                             |  |

| net a<13> loc=p57; # RAM address pin A13                              |  |

| net a<14> loc=p61;  # RAM address pin A14                             |  |

| net a<15> loc=p34;  # RAM address pin A15                             |  |

| net a<16> loc=p74;  # RAM address pin A16                             |  |

| net we_n loc=p63; # RAM write-enable                                  |  |

| net oe_n loc=p62;                                                     |  |

|                                                                       |  |

© 2001 by XESS Corp.

```

net ce_n loc=p65; # RAM chip-enable

net s<0> loc=p21; # LED segment S0

net s<1> loc=p23; # LED segment S1

net s<2> loc=p19; # LED segment S2

net s<3> loc=p17; # LED segment S3

net s<4> loc=p18; # LED segment S4

net s<5> loc=p14; # LED segment S5

net s<6> loc=p15; # LED segment S6

```

#### Listing 7: Pin assignments for the XS40 Board.

| <pre># pin assignments f</pre>      |                                         |

|-------------------------------------|-----------------------------------------|

|                                     | clock from programmable osc.            |

|                                     | reset from data pin D0 of parallel port |

| net d<0> loc=p41; #                 |                                         |

| net d<1> loc=p40; #                 |                                         |

| net d<2> loc=p40; #                 |                                         |

| net d<3> loc=p38; #                 | -                                       |

| net d<4> loc=p30; #                 | -                                       |

| net d<5> loc=p81; #                 | -                                       |

| net d<6> loc=p80; #                 | -                                       |

| net d<7> loc=p10; #                 | -                                       |

| <pre>net a&lt;0&gt; loc=p3; #</pre> | -                                       |

| net a<1> loc=p4; #                  |                                         |

| net a<2> loc=p5; #                  |                                         |

| net a<3> loc=p78; #                 |                                         |

| net a<4> loc=p79; #                 |                                         |

| net a<5> loc=p82; #                 |                                         |

| net a<6> loc=p83; #                 | RAM address pin A6                      |

| net a<7> loc=p84; #                 | RAM address pin A7                      |

| net a<8> loc=p59;#                  | RAM address pin A8                      |

| net a<9> loc=p57;#                  | -                                       |

| ±                                   | # RAM address pin A10                   |

|                                     | # RAM address pin All                   |

|                                     | # RAM address pin A12                   |

|                                     | # RAM address pin A13                   |

|                                     | # RAM address pin A14                   |

| —                                   | # RAM address pin A15                   |

|                                     | # RAM address pin A16                   |

| <pre>net we_n loc=p62; #</pre>      |                                         |

| <pre>net oe_n loc=p61; #</pre>      |                                         |

| <pre>net ce_n loc=p65; #</pre>      | -                                       |

| net s<0> loc=p25; #                 |                                         |

| net s<1> loc=p26; #                 |                                         |

| net s<2> loc=p24; #                 | -                                       |

| net s<3> loc=p20; #                 | -                                       |

| net s<4> loc=p23; #                 | -                                       |

| net s<5> loc=p18; #                 | -                                       |

| net s<6> loc=p19; #                 | LED segment S6                          |

Once the target device, top-level module, implementation options and constraint file are setup, click on the Run button to start the synthesis and implementation phases.

| Synthesis/Impl   | ementation    | settin   | gs        | ×               |

|------------------|---------------|----------|-----------|-----------------|

| Top level:       | ramsum        |          | •         | <u>R</u> un     |

| Version name:    | ver1          |          |           | ОК              |

| Synthesis Settin | gs:           | 9        | SET       | <u>C</u> ancel  |

|                  |               |          |           | <u>H</u> elp    |

| F Target Device  |               |          |           |                 |

| Family: XC9      | 500           | •        |           |                 |

| Device: 9510     | )8PC84        | -        | Speed:    | -20 💌           |

| Edit Synthesi    | s/Implementa  | tion cor | nstraints |                 |

| View Estimat     | ed Performan  | ce after | Optimiza  | ation           |

| 🔽 Auto Run I     | mplementation | n tools  |           |                 |

| - Physical Imple |               |          |           |                 |

| Revis            | ion name:     | rev1     |           | <u>O</u> ptions |

| Contro           | ol Files:     | SE       | T         |                 |

|                  |               |          |           |                 |

Both phases should complete with no problems.

| Project Manager 🛛 🔀                            |

|------------------------------------------------|

| Flow Engine ver1->rev1 Completed Successfully. |

| ОК                                             |

#### Generating the Bitstream

Once the implementation phase is completed, we can go on to create the SVF file containing the configuration bitstream for the XC95108 CPLD.

Select the Output→Create SVF File... menu item from the **JTAG Programmer** window that appears.

| 🞇 dsgn5_1 - JTAG Programmer                                 | _ 🗆 🗵    |

|-------------------------------------------------------------|----------|

| <u>File Edit Operations Output View Help</u>                |          |

| □ 🖙 🖬 🐰 📴 Cable Auto Connect 🚼 🖽 🛱 🖽 🤹 🎖 🕺                  |          |

|                                                             |          |

| Cable <u>R</u> eset                                         | -        |

| V Use Cable                                                 |          |

| Create SVF File                                             |          |

| Append to SVF File                                          |          |

|                                                             |          |

| XC95108                                                     |          |

| dsgn5_1.jed                                                 |          |

|                                                             |          |

| TDO                                                         |          |

|                                                             |          |

|                                                             |          |

|                                                             | <b>⊁</b> |

| Creates an SVF file and directs subsequent operations to it |          |

As always, specify an initial transition of the JTAG state machine through the Test-Logic-Reset state.

| SVF Options               |                | ×            |

|---------------------------|----------------|--------------|

| Initial transition to F   | Run-Test/Idle: |              |

| Through Test-L            | .ogic-Reset    |              |

| C <u>S</u> kipping Test-I | _ogic-Reset    |              |

| ок                        | Cancel         | <u>H</u> elp |

Then tell the JTAG Programmer to save the configuration bitstream in the dsgn5\_1.svf file in the top-level directory of the **dsgn5\_1** project.

| Create a New SVF File          |       | ? ×          |

|--------------------------------|-------|--------------|

| Save in: 🗀 dsgn5_1             | - 🗈 🜌 | 🗃 🔳          |

| 🗋 dpm_net                      |       |              |

| 🚊 dsgn5_1                      |       |              |

| ib .                           |       |              |

| xproj                          |       |              |

| lagn5_1.svf                    |       |              |

|                                |       |              |

|                                |       |              |

| File name: dsgn5_1.svf         | <br>  | <u>S</u> ave |

| Save as type: SVF Files(*.svf) | •     | Cancel       |

Now initiate the generation of the bitstream by selecting the Operations  $\rightarrow$  Program menu item.

| 🏪 dsgn5j                  | 1 - JTAG Programmer                   |          |

|---------------------------|---------------------------------------|----------|

| <u>F</u> ile <u>E</u> dit | Operations Output View Help           |          |

|                           | Program<br>Verify                     |          |

|                           | <u>E</u> rase                         | <b>▲</b> |

|                           | Eunctional Test                       |          |

|                           | Blank Check                           |          |

|                           | <u>R</u> eadback Jedec                |          |

| I I                       | Get Device <u>I</u> D                 |          |

| TDI                       | Get Device Checksum                   |          |

|                           | Get Device <u>S</u> ignature/Usercode |          |

|                           | Chain <u>O</u> perations              |          |

|                           | dsgn5_1.jed                           |          |

|                           |                                       |          |

| TDO -                     |                                       |          |

|                           |                                       |          |

|                           |                                       | -        |

| •                         |                                       | <u> </u> |

| Programs th               | ne selected devices in the JTAG chain | SVF Mode |

Just click on the OK button in the **Options** window to begin generating the bitstream.

| Options                           | ×                       |

|-----------------------------------|-------------------------|

| Program Options                   |                         |

| Erase Before Programmin           | 🖵 Skip user array       |

| I ⊻erify                          | ☐ <u>W</u> rite Protect |

| Eunctional Test                   | Read Protect            |

| Parallel Modi                     | 🗖 Load Fpga             |

| External <u>P</u> in Verification | 1 Pin #:                |

| Usercode (8 Hex Chars             | j FFFFFFF               |

|                                   |                         |

|                                   |                         |

| ок 🖓                              | Cancel <u>H</u> elp     |

The bitstream generation should complete without incident.

| Operation Status                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ×   |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Loading Boundary-Scan Description Language (BSDL) file<br>'C:/Fndtn/xc9500/data/xc95108.bsd'completed successfully.<br>'dsgn5_1(Device1)': Generating SVF vectors to check boundary-scan chain<br>integritydone.<br>'dsgn5_1(Device1)': Generating SVF vectors to put device in ISP modedone.<br>'dsgn5_1(Device1)': Generating SVF vectors to erase devicedone.<br>'dsgn5_1(Device1)': Processing JEDEC filedone.<br>'dsgn5_1(Device1)': Generating SVF vectors to program devicedone.<br>'dsgn5_1(Device1)': SVF vector generation for programming completed successfully. | A F |

| All operations were completed successfully.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     |

| OK View Log File                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     |

#### Downloading and Testing the Design

We need some test data to store into the RAM of the XS95 Board in order to test the design. Go to the top-level directory of the *dsgn5\_1* project and use a text editor to create a file called data.hex containing this single line of text:

- OB 0000 FF FE FD FC FB FA F9 F8 F7 F6 F5  $\,$

This is a set of eleven data bytes that will be loaded into RAM starting at address zero. (This data is represented in the XESS format.) If you manually complement-and-sum these data values you will get the following result (in two-digit hexadecimal):

```

(-FF) + (-FE) + (-FD) + (-FC) + (-FB) + (-FA) + (-F9) + (-F8) + (-F7) + (-F6) + (-F5) =

(1) + (2) + (3) + (4) + (5) + (6) + (7) + (8) + (9) + (A) + (B) =

42

```

Now that the SVF and test data file are ready, connect an XS95 Board to the PC parallel port and start the GXSLOAD program. Go to the top-level directory for the **dsgn5\_1** project and select the dsgn5\_1.svf and data.hex files. Then drag-and-drop them into the **gxsload** window. The data file will be downloaded into the RAM and then the SVF file will be programmed into the XC95108 CPLD on the XS95 Board.

| 🔀 gxsload 📃 💌                                                                                         | 🖿 dsgn5_1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|-------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Drop .BIT, .SVF, .HEX, and .EX0<br>files here to download to the<br>XS or XSV Board.<br>Recent Files: | File     Edit     View     Go     Favorites     Help       ↓     ↓     ↓     ↓     ↓     ↓       ↓     ↓     ↓     ↓     ↓       ↓     ↓     ↓     ↓     ↓       ↓     ↓     ↓     ↓     ↓       ↓     ↓     ↓     ↓     ↓       ↓     ↓     ↓     ↓     ↓       ↓     ↓     ↓     ↓     ↓       ↓     ↓     ↓     ↓     ↓       ↓     ↓     ↓     ↓     ↓                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                       | Image: Second secon                |

| Reload EEPROM Port LPT1                                                                               | Image: Second |

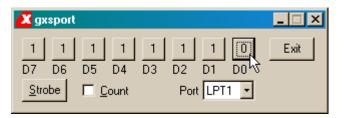

The reset for the circuit is controlled by data pin D0 of the parallel port. If D0 is at logic 1 after the downloading completes, the circuit will be held in the reset state and the LED will be blank. To release the reset, open the **gxsport** window and click on the D0 button until it displays a zero.

Then click on the Strobe button so the logic 0 value is output on the D0 pin of the parallel port.

| 🔼 дхѕро                | rt |      |             |    | _ 🗆 🗵 |

|------------------------|----|------|-------------|----|-------|

| 1 1<br>D7 D6<br>Strobe |    |      | <br>        | D0 | Exit  |

|                        |    | Jank | <br>. jer i | ·  |       |

The answer is that you are probably running the design with a 50 MHz clock (the default for the XS95 Board). Can this design run that fast? Let's check the timing for the implemented design. Click on the icon for the report files in the **Project Navigator** window.

| 📣 dsgn5_1 - ver1 (95108-20PC)                        | 84) - Project Manager                                      | _ 🗆 × |  |

|------------------------------------------------------|------------------------------------------------------------|-------|--|

| <u>File D</u> ocument <u>View Project S</u>          | ynthesis <u>I</u> mplementation <u>T</u> ools <u>H</u> elp |       |  |

|                                                      |                                                            |       |  |

| Files Versions                                       | Flow Contents Reports                                      |       |  |

| 🖻 🗖 dsgn5_1                                          |                                                            | -     |  |

| 🕀 🗳 leddod.vhd                                       | ver1 rev1 (XC95108-20-PC84)                                |       |  |

| 🕀 🚭 ramsum.vhd                                       |                                                            |       |  |

| - 🖯 dsgn5_1<br>- 🖯 simprims                          | 🖺 📲 🌄 🏣 🛛                                                  |       |  |

| ⊖ xc9500                                             |                                                            |       |  |

|                                                      |                                                            |       |  |

|                                                      | 100 L                                                      |       |  |

|                                                      |                                                            |       |  |

|                                                      | SYNTHESIS SIMULATION                                       |       |  |

|                                                      |                                                            |       |  |

|                                                      |                                                            |       |  |

|                                                      | IMPLEMENTATION VERIFICATION                                | -     |  |

| Pcm : Synopsys version: 3, 3, 1                      | 0, 4517                                                    | -     |  |

| Pcm : Reading Synopsys/Xilin                         |                                                            |       |  |

| Console / HDL Errors / HDL Warnings / HDL Messages / |                                                            |       |  |

|                                                      | nings / HDL Messages /                                     |       |  |

| Ready                                                |                                                            |       |  |

Then double-click the Post Layout Timing Report in the **Report Browser** window.

| 🚯 Report Browser - dsgn5_1(ver1->rev1) |                |                              | × |

|----------------------------------------|----------------|------------------------------|---|

|                                        |                | Ď                            |   |

| Translation<br>Report                  | Fitting Report | Post Layout<br>Timing Report |   |

The top portion of the timing report is shown in Listing 8 and this tells us what we want to know: the maximum clock frequency for this design is 5.5 MHz. The slow clock is brought about by the long carry propagation times through the complementors and adders in the design. The situation is made worse because the implementation algorithms have packed the logic to emphasize area efficiency and this can add extra propagation delays to the circuit.

#### Listing 8: Timing report for the design.

Performance Summary Report

Design: dsqn5 1 Device: XC95108-20-PC84 Program: Timing Report Generator: version C.22 Date: Sat Jan 05 14:08:28 2002 Performance Summary: Clock net 'clk' path delays: Clock Pad to Output Pad (tCO): 73.0ns (4 macrocell levels) Clock Pad 'clk' to Output Pad 's<4>' (GCK) 161.5ns (8 macrocell levels) Clock to Setup (tCYC): Clock to Q, net 'sum r<0>.Q' to TFF Setup(D) at 'sum r<7>.D' (GCK) Target FF drives output net 'sum r<7>' Setup to Clock at the Pad (tSU): 151.5ns (7 macrocell levels) Data signal 'd<0>' to TFF D input Pin at 'sum r<7>.D' Clock pad 'clk' (GCK) Minimum Clock Period: 161.5ns Maximum Internal Clock Speed: 6.1Mhz (Limited by Cycle Time)

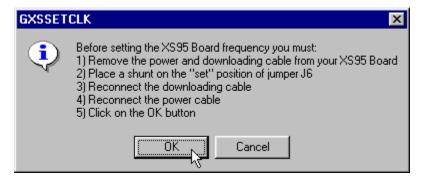

We need to reduce the clock frequency of the XS95 Board to less that 6.1 MHz in order for our design to work reliably. To do this, start the GXSSETCLK program. Place 20 in the Divisor field to reduce the 100 MHz master frequency to 5 MHz. Then click on the SET button.

| 者 Set XS B | oard Clock Frequ                            | ency 📃 🗖 🗙     |

|------------|---------------------------------------------|----------------|

| Board Type | XS95-108 💌                                  | SET            |

| Port       | LPT1 💌                                      | Exit           |

| Divisor    | 20                                          | External Clock |

|            | oard clock frequency<br>100 MHz master free |                |

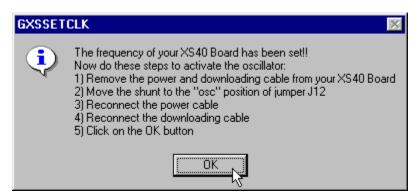

A set of instructions will appear that must be followed to adjust the clock frequency of the XS95 Board. After doing these steps, click on the OK button to reprogram the clock.

Reprogramming the clock takes a minute or two after which the following set of instructions is given to activate the new clock frequency.

| GXSSET | GXSSETCLK 🛛 🕅                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| •      | The frequency of your XS95 Board has been set!!<br>Now do these steps to activate the oscillator:<br>1) Remove the power and downloading cable from your XS95 Board<br>2) Move the shunt to the "osc" position of jumper J6<br>3) Reconnect the power cable<br>4) Reconnect the downloading cable<br>5) Click on the OK button |  |  |  |  |  |

|        |                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

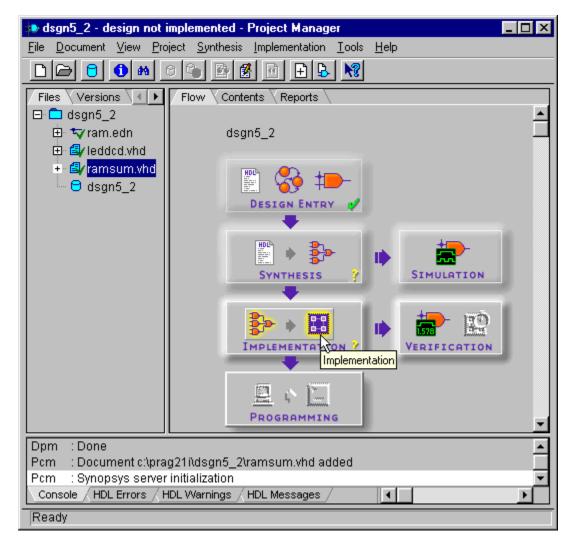

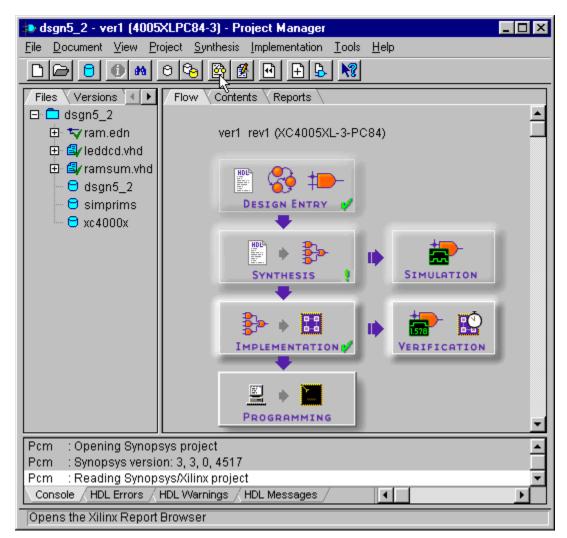

# Using an Internal Synchronous RAM

The second version of the RAM summation circuit has the design hierarchy shown in Figure 15. The root module of the design sums the data stored in an internal synchronous RAM module while the LED decoder module displays the four-bit hexadecimal digits on a seven-segment display. Only the XC4000 FPGAs have internal RAM so this design can only be done using the XS40 Board. The XC95108 CPLD on the XS95 Board is not suitable for designs, which require large amounts of internal data storage.

Figure 15: Design hierarchy for a logic circuit that displays the summation of data in an internal synchronous RAM.

Each of these modules is stored in the *dsgn5\_2* directory that was created by starting an HDL project follows.

| New Proje  | X                   |       |              |

|------------|---------------------|-------|--------------|

| Name:      | DSGN5_2             |       | ок           |

| Directory: | C:\PRAG211          |       | Cancel       |

| Туре:      | F2.1i               | •     | <u>H</u> elp |

| Flow:      | C <u>S</u> chematic | ● HDL |              |

#### The Internal RAM Module

The first module we will add is the internal synchronous RAM. This module is constructed using the CORE Generator. To start this tool, select the Tools→Design Entry→Core Generator... menu item.

| 🐌 dsgn5_2 - design i                      | not implemented - Project Manag                       | er 💶 🗙                       |

|-------------------------------------------|-------------------------------------------------------|------------------------------|

| <u>File</u> <u>D</u> ocument <u>V</u> iew | Project Synthesis Implementation                      | <u>I</u> ools <u>H</u> elp   |

|                                           | S <u>c</u> hematic Editor                             | <u>D</u> esign Entry ►       |

|                                           | State E <u>d</u> itor                                 | Simulation/Verification      |

| Files Versions                            | <u>H</u> DL Editor                                    | Implementation               |

| □ □ dsgn5_2                               | Symbol <u>E</u> ditor                                 | Device <u>P</u> rogramming ► |

| <sup>l</sup> <mark>⊖</mark> dsgn5_2       | LogiBLOX module generator                             | Utilities                    |

|                                           | <u>C</u> ORE Generator                                |                              |

|                                           |                                                       | -                            |

|                                           | DESIGN ENTRY                                          | Ŷ                            |

|                                           | •                                                     |                              |

|                                           |                                                       |                              |

|                                           | SYNTHESIS                                             | SIMULATION                   |

|                                           | -                                                     |                              |

|                                           | 影 (四)                                                 | 1. to to                     |

|                                           |                                                       |                              |

|                                           | IMPLEMENTATION                                        | VERIFICATION                 |

|                                           |                                                       |                              |

|                                           |                                                       |                              |

|                                           | PROGRAMMING                                           |                              |

|                                           |                                                       | •                            |

|                                           | \prag21i\dsgn5_2\ram.edn added<br>rver initialization | <u> </u>                     |

|                                           | \prag21i\dsgn5_2\ram.edn remov                        | ed 🗸                         |

|                                           | / HDL Warnings / HDL Messages /                       |                              |

| Run CoreGen                               |                                                       |                              |

The **Xilinx CORE Generator** window will appear. The left-hand pane of the window displays the various families of circuits that the tool can generate. The individual circuits within a highlighted family are shown in the right-hand pane.

| Elle Project Corre Web Help     Project Path: C:\Prag21i\dsgn5_2 Target Family: SPARTAN     View mode: Taxonomy     Contents of:     Basic Elements   Communication & Networking   Digital Signal Processing   Math Functions   Math Functions   Math Functions   ProtoType & Development Hardware Products   Standard Bus Interfaces   Storage Elements & Memories                                |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| View mode: Taxonomy       Contents of:         Basic Elements       Name       Type       Version       Family         Digital Signal Processing       Math Functions       Microprocessors, Controllers & Peripherals       ProtoType & Development Hardware Products         Standard Bus Interfaces       Standard Bus Interfaces       Standard Bus Interfaces       Standard Bus Interfaces   |

| View mode: Taxonomy       Contents of:         Image: Basic Elements       Name       Type       Version       Family         Image: Digital Signal Processing       Math Functions       Image: Basic Controllers & Peripherals       Image: Basic Controllers & Peripherals         Image: ProtoType & Development Hardware Products       Standard Bus Interfaces       Standard Bus Interfaces |

| Basic Elements       Name       Type       Version       Family         Digital Signal Processing       Microprocessors, Controllers & Peripherals       ProtoType & Development Hardware Products         Standard Bus Interfaces       Standard Bus Interfaces       Standard Bus Interfaces                                                                                                     |

| Communication & Networking     Digital Signal Processing     Math Functions     Microprocessors, Controllers & Peripherals     ProtoType & Development Hardware Products     Standard Bus Interfaces                                                                                                                                                                                               |

| Digital Signal Processing     Math Functions     Microprocessors, Controllers & Peripherals     ProtoType & Development Hardware Products     Standard Bus Interfaces                                                                                                                                                                                                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                                                                                                                                                                                                                                                                                    |

Our first action is to setup the CORE Generator for the target FPGA and type of project we are using in Foundation. Click on the Project → Project Options... menu item to open the **Project Options** window.