# **XSA Parallel Port Interface**

March 17, 2004 (Version 1.1)

Application Note by D. Vanden Bout

# Summary

This application note describes the default parallel port interface circuit that is programmed into the XC9572XL CPLD on the XSA Board. It also discusses how to change the parallel port interface to support other features.

### The Default Parallel Port Interface

Listing 1 shows the VHDL code for the default parallel port interface that is programmed into the XC9572XL CPLD on the XSA Board. This interface provides two functions:

- It transfers configuration bitstreams from the PC to the SpartanII FPGA.

- It lets the PC and the SpartanII communicate through the parallel port after the FPGA is configured.

How the VHDL implements these functions is described below.

Lines 39–42 disable other chips and functions on the XSA Board so they cannot interfere with the configuration of the SpartanII device. The JTAG circuitry of the SpartanII FPGA is kept quiescent by holding its clock pin low on line 42. The Flash RAM is disabled by pulling its chip-enable pin high on line 43. The Flash chip-enable is allowed to float once the SpartanII device is configured (as indicated when the SpartanII DONE pin goes high) so the SpartanII can take control of the Flash chip-enable.

The circuitry that actually controls the configuration of the SpartanII device is described on lines 45-62. The CPLD pulls down the M0 mode pin of the SpartanII device to set the FPGA into the Slave Parallel configuration mode (the M1 and M2 mode pins of the SpartanII are hard-wired on the XSA The PROGRAM pin for the Spartanll is connected to data line D7 of the parallel port on line 48. A low level on D7 will initiate the configuration of the SpartanII and its DONE pin will go low. The low level on the DONE pin forces low levels on the chipselect and write-strobe of the SpartanII on lines 49-50. This enables the writing of byte-wide configuration data into the SpartanII. These pins are released after DONE goes high because they

become general-purpose I/O pins after configuration is completed.

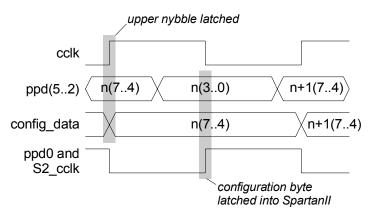

The configuration data bytes arrive as two four-bit nybbles over data lines D2–D5. The upper nybble of each configuration byte is stored in the config\_data register on the rising edge of the cclk (lines 57–62). The inverse of parallel port data line D0 drives the internal cclk signal, so the data is latched into the config\_data register on the falling edge of D0.

The upper nybble in the config\_data register is concatenated with the lower nybble on the D2–D5 data lines to form a complete byte of configuration data. This configuration data is passed to the SpartanII on line 53. The configuration clock for the SpartanII is the inverse of the clock that controls the config\_data register (line 52). So the configuration data is latched into the SpartanII on the falling edge of cclk. The overall process of getting byte n of configuration data into the SpartanII looks like this:

Once all the configuration data enters the SpartanII, it will raise its DONE pin. This will raise the chip-select and write-strobe of the SpartanII (lines 49–50) and disable further writing of configuration data. It will also make the CPLD release control of the SpartanII configuration data input pins (lines 54 and 55).

These pins become general purpose I/O pins after DONE goes high and the FPGA can use them to access data from the Flash or to drive the seven-segment LED. If the SpartanII is not accessing the Flash (i.e., the Flash chip-enable, fceb, is high) then the CPLD will light up the decimal-point segment of the LED to indicate that the SpartanII is currently configured while releasing the remaining data lines (line 54). But if the SpartanII enables the Flash, then the CPLD releases all the data lines to prevent contention with the FPGA (line 55).

Lines 65 and 66 describe how the CPLD connects the parallel port data lines to the general-purpose I/O pins of the SpartanII. Line 65 connects the eight parallel port data lines to the SpartanII so it can receive data from the PC. (The lower two data bits are inverted to mimic the parallel port connection used by the XS95, XS40 and XSV Boards.) These same FPGA pins are used by the SpartanII to connect to address pins A8–A13, the write-enable and the output-enable of the Flash. Therefore, the CPLD releases these pins to avoid contention when the SpartanII lowers the Flash chip-enable and begins to access the Flash.

On line 66 the CPLD connects three of the parallel port status lines to the SpartanII so the FPGA can transfer data back to the PC. The SpartanII also has a direct connection to a fourth status line. (The CPLD uses the fifth status line for the TDO output of its JTAG interface, so it is not available for general-purpose transfer of data to the PC.)

Finally, the CPLD connects the output of the programmable oscillator on the XSA Board to a dedicated clock input of the SpartanII (line 69).

The default parallel port interface implements the following connections between the SpartanII and the parallel port, LED and programmable oscillator.

| Pin Function                | Spartanll Pin# |

|-----------------------------|----------------|

| Parallel Port Data Pin D0   | 50             |

| Parallel Port Data Pin D1   | 48             |

| Parallel Port Data Pin D2   | 42             |

| Parallel Port Data Pin D3   | 47             |

| Parallel Port Data Pin D4   | 65             |

| Parallel Port Data Pin D5   | 51             |

| Parallel Port Data Pin D6   | 58             |

| Parallel Port Data Pin D7   | 43             |

| Parallel Port Status Pin S3 | 40             |

| Parallel Port Status Pin S4 | 29             |

| Parallel Port Status Pin S5 | 28             |

| Parallel Port Status Pin S6 | 78             |

| LED Segment S0              | 67             |

| LED Segment S1              | 39             |

| LED Segment S2              | 62             |

| LED Segment S3              | 60             |

| LED Segment S4              | 46             |

| LED Segment S5              | 57             |

| LED Segment S6              | 49             |

| LED Segment DP              | 44             |

| Programmable Oscillator     | 88             |

# **Changing the Parallel Port Interface**

The parallel port interface is stored in the nonvolatile Flash of the XC9572XL CPLD on the XSA Board. Any design you load into the CPLD will become active as soon as the XSA Board powers up. So it is possible to load a faulty interface design into the CPLD that makes it impossible to program the SpartanII even after you cycle the power. The only solution is to explicitly reprogram the CPLD with a functional interface using GXSLOAD. Then the XSA Board will function correctly again.

When generating a new interface for the CPLD, you must set the USERCODE signature register to the four-character string <4>!. The XSTOOLs utilities look for this signature in the CPLD to verify that a valid interface is present.

There are probably only three things you might want to change in the default parallel port interface:

You might want to give the Spartanll access to the decimal-point of the seven-segment LED instead of having the CPLD use it to display the configuration status of the FPGA. To do this, change the bitstring on line 54 to "ZZZZZZZZZ". Note that once you do this you

- will no longer get any visual indication of whether your SpartanII bitstreams were downloaded correctly into the FPGA.

- 2. You might want to use all eight parallel port data pins to send data to the SpartanII. Therefore you will have to prevent any data presented on bit D7 from affecting the PROGRAM pin of the SpartanII or it will erase its configuration. You could connect the PROGRAM pin to a constant logic '1' and then you would have to interrupt the power to the XSA Board to force a reconfiguration.

- 3. You might want to change the clock that is passed to the Spartanll on line 69. You can pass the programmable oscillator output through a divider and on to the Spartanll. Or you could drive the Spartanll clock input with one of the parallel port data pins to do single-stepping of a design. Or you could have the CPLD release the Spartanll clock input entirely so you can drive it with an external clock source.

1

2

3

5

6

7

8

9

11

12 13

14

15

16

17

18

32

40 41 42

43

44 45

46

47

48

49

50

51

52

53

54

55

56 57

58 59

60

61

62

### Listing 1: VHDL code for the default CPLD parallel port interface.

```

library ieee;

use ieee.std logic 1164.all;

entity dwnldpar is

port(

-- parallel port data and status pins

ppd: in std_logic_vector(7 downto 0);

pps: out std logic vector (5 downto 3);

-- programmable oscillator

clk: in std logic;

-- Spartan2 FPGA pins

S2 tck: out std logic; -- driver to Spartan2 JTAG clock

S2 cclk: out std logic; -- driver to Spartan2 config clock

S2 progb: out std logic; -- driver to Spartan2 program pin

S2 csb: out std logic; -- driver to Spartan2 config. chip-select

S2 wrb: out std logic; -- driver to Spartan2 config. write strobe

S2_initb: in std_logic; -- input from Spartan2 init pin

S2_done: in std_logic; -- input from Spartan2 done pin

S2_d: out std_logic_vector(7 downto 0); -- drivers to Spartan2 data pins and 7-seg LED

S2_m: out std_logic_vector(0 downto 0); -- Spartan2 config mode pins

S2 clk: out std logic; -- clock output to Spartan2

S2_ppd: out std_logic_vector(7 downto 0); -- parallel port data pins to Spartan2 S2_pps: in std_logic_vector(5 downto 3);-- parallel port status pins from Spartan2

fceb: inout std_logic -- Flash chip-enable

);

end entity dwnldpar;

architecture arch of dwnldpar is

constant LO: std logic := '0';

constant HI: std logic := '1';

constant SLAVE_PARALLEL_MODE: std_logic_vector(0 downto 0) := "0";

signal cclk: std logic;

signal config_data: std_logic_vector(3 downto 0);

component pullup port(O: out std logic); end component;

-- disable other chips on the XSV Board so they don't interfere

-- during the configuration of the Spartan2 FPGA

S2 tck

<= LO; -- deactivate Spartan2 JTAG circuit

<= HI when S2 done=LO else 'Z'; -- disable Flash during config.

-- connect Spartan2 configuration pins

<= SLAVE PARALLEL MODE; -- set Spartan2 config mode pins</pre>

u0: pullup port map(O=>S2_progb); -- place a pullup on the Spartan2 PROGRAM pin

S2_{progb} \le L0 \text{ when } ppd(\overline{7}) = L0 \text{ else 'Z'}; -- programming pulse comes from parallel port

S2_csb

<= LO when S2_done=LO else 'Z'; -- enable writing of data</pre>

S2_wrb

<= LO when S2_done=LO else 'Z'; -- during Spartan2 config. phase</pre>

cclk

\leq not ppd(0);

S2 cclk

<= not cclk;

s2_d

<= (config_data & ppd(5 downto 2)) when S2_done=LO else

"ZZZZZZZIZ" when fceb=HI else -- show Spartan2 config status on LED-DP

"ZZZZZZZZ"; -- release control of Spartan2 Flash/LED pins

process (cclk)

if(cclk'event and cclk=HI) then

config data <= ppd(5 downto 2);</pre>

end if;

end process;

```

```

-- connect the parallel port data and status pins to the Spartan2

S2_ppd <= (ppd(7 downto 2) & not(ppd(1 downto 0))) when fceb=HI else "ZZZZZZZZZ";

pps <= S2_pps;

-- send the programmable oscillator clock to the Spartan2

S2_clk <= clk;

end architecture arch;</pre>

```

# Listing 2: User-constraint file for CPLD pin assignments.

```

1

2

# pin assignments for the XC9572XL CPLD chip on the XSA Board

3

4

5

6

# Spartan2 FPGA connections to CPLD

net S2_clk

loc=p42;

7

net S2_tck

loc=p13;

8

# net S2_dout

# net S2_din

loc=p18;

9

loc=p2;

10

net S2 wrb

loc=p19;

11

net S2 csb

loc=p15;

12

# net S2 initb

loc=p38;

13

net S2 done

loc=p40;

net S2_progb

14

loc=p39;

15

net S2 cclk

loc=p16;

16

net S2 m<0>

loc=p36;

17

net S2 d<0>

loc=p2;

18

net S2 d<1>

loc=p4;

19

net S2_d<2>

loc=p5;

20

21

net S2_d<3>

loc=p6;

\mathtt{net} \ \mathtt{S2\_d} {<} \mathtt{4} {>}

loc=p7;

22

net S2_d<5>

net S2_d<6>

loc=p8;

23

loc=p9;

24

net S2 d<7>

loc=p10;

25

26

27

28

net S2 ppd<0>

loc=p45;

net S2_ppd<1>

loc=p44;

loc=p57;

net S2_ppd<2>

net S2 ppd<3>

loc=p43;

29

net S2 ppd<4>

loc=p56;

30

net S2 ppd<5>

loc=p46;

31

net S2 ppd<6>

loc=p49;

32

net S2 ppd<7>

loc=p12;

33

net S2 pps<3>

loc=p1;

34

net S2_pps<4>

loc=p64;

35

net S2_pps<5>

loc=p63;

36

37

# Flash RAM

38

# net fd<0>

loc=p2;

39

# net fd<1>

loc=p4;

40

# net fd<2>

loc=p5;

41

# net fd<3>

loc=p6;

42

# net fd<4>

loc=p7;

43

# net fd<5>

loc=p8;

44

# net fd<6>

loc=p9;

45

# net fd<7>

loc=p10;

46

# net fa<0>

loc=p1;

47

# net fa<1>

loc=p64;

48

# net fa<2>

loc=p63;

49

# net fa<3>

loc=p62;

50

# net fa<4>

loc=p61;

51

# net fa<5>

loc=p60;

52

# net fa<6>

loc=p59;

53

# net fa<7>

loc=p58;

54

# net fa<8>

loc=p45;

55

loc=p44;

# net fa<9>

56

loc=p57;

# net fa<10>

57

# net fa<11>

loc=p43;

58

# net fa<12>

loc=p56;

59

# net fa<13>

loc=p46;

60

# net fa<14>

loc=p47;

61

# net fa<15>

loc=p52;

62

# net fa<16>

loc=p51;

```

#### XSA Parallel Port Interface

```

63

# net fa<17>

loc=p48;

64

# net frstb

loc=p50;

# Flash reset

65

# net foeb

loc=p12; # Flash output-enable

66

# net fweb

loc=p49; # Flash write-enable

67

net fceb

loc=p11; # Flash chip-enable

68

69

# DIP and pushbutton switches

70

# net dipsw<1> loc=p47;

71

# net dipsw<2>

loc=p52;

72

# net dipsw<3>

loc=p51;

73

# net dipsw<4>

loc=p48;

74

75

# 7-segment LEDs

76

# net s<0>

loc=p10;

77

# net s<1>

loc=p2;

78

loc=p9;

# net s<2>

loc=p8;

79

# net s<3>

80

# net s<4>

loc=p5;

81

# net s<5>

loc=p7;

82

# net s<6>

loc=p6;

83

# net dp

loc=p4;

84

85

# programmable oscillator

86

net clk

loc=p17;

87

88

# parallel port

89

loc=p33;

net ppd<0>

90

net ppd<1>

loc=p32;

91

net ppd<2>

loc=p31;

92

net ppd<3>

loc=p27;

93

net ppd<4>

loc=p25;

94

net ppd<5>

loc=p24;

95

net ppd<6>

loc=p23;

96

net ppd<7>

loc=p22;

97

loc=p34;

net pps<3>

98

net pps<4>

loc=p20;

99

net pps<5>

loc=p35;

```