# Configuring the Audio Codec on the XSB-300E Board

November 15, 2003 (Version 1.0)

Application Note by D. Vanden Bout

## Summary

This application note describes the circuitry and software that are used to configure the AK4565 audio codec on the XSB-300E Board.

#### Introduction

The XSB-300E Board processes stereo audio signals with its AK4565 codec chip. The AK4565 has many programmable options that are controlled by setting values into the registers within the chip. The registers are loaded through a serial interface.

It can be daunting to design the interface circuit to the registers and the state machine that loads the appropriate register values in addition to designing the signal processing circuitry that handles the data streaming to and from the codec. Therefore, XESS provides a simple PC-based utility, GXSSETCODEC, that allows you to initialize the codec registers. Once initialized, the registers will retain their values until power to the XSB-300E Board is interrupted. After the codec is initialized, you can download your FPGA bitstream file that configures the FPGA for audio data stream processing.

GXSSETCODEC employs a two-phase operation:

Phase 1: The FPGA is configured with a bitstream that creates a path from the the PC parallel port to the serial register interface pins of the audio codec.

Phase 2: A GUI is used to select the desired register values that are then downloaded into the codec through the parallel port.

## **Codec Parallel Port Interface**

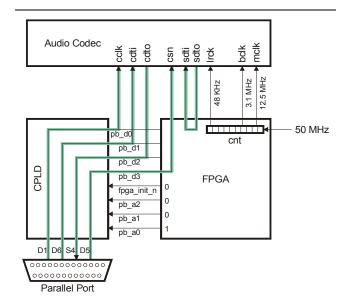

A high-level schematic for the parallel port interface to the audio codec is shown in Figure 1.

Figure 1: Codec parallel port interface schematic.

Listing 1 shows the VHDL code for the default parallel port interface that is programmed into the XC9572XL CPLD on the XSB-300E Board. Lines 68-72 are responsible for the parallel port interface to the audio codec. This circuitry is activated after the FPGA is configured and the FPGA lowers the the fpga init n line and places the bitstring "001" onto the lower three bits of the peripheral bus (pb a(2:0)) as described by lines 27-28 of Listing 3. The chipselect for the codec is connected to bit D5 of the parallel port through the CPLD and FPGA. Data bit D1 of the parallel port drives the clock pin of the codec register interface while data bit D6 connects to the serial data input pin. Serial data output from the codec arrives back at the PC through the S4 status pin of the parallel port.

The FPGA also implements a simple loopback circuit that allows you to pass an audio signal through the

codec and listen to it to gauge the effect of changing the configuration registers. This loopback is accomplished by piping the digitized output from the codec back into its input. The necessary codec clock signals are generated from a ten-bit counter that is clocked by the 50 MHz output of the programmable oscillator chip on the XSB-300E Board.

# **GXSSETCODEC Graphical User Interface**

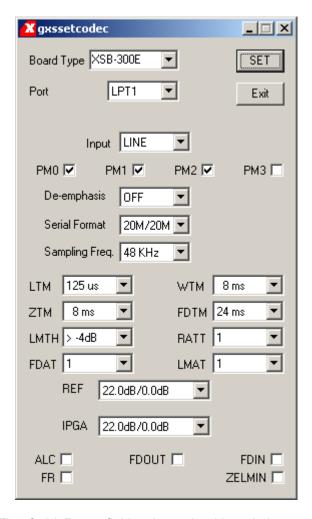

The GXSSETCODEC utility is started by clicking on

the gxssetcodec window will appear as shown below. Set the Board Type field to XSB-300E since this is the only board from XESS that uses the AK4565 codec and GXSSETCODEC will not work with any of the other XESS boards. Then set the Port field to LPT1, LPT2 or LPT3 depending upon what parallel port the XSB-300E is connected to. Finally, click on the SET button to load the FPGA with the bitstream for configuring the codec through the parallel port.

The codec registers are also initialized at this time with the default values shown in the window. Any further changes to the codec option settings will be immediately loaded into the codec registers. The effect of the settings for the various codec options will now be discussed.

The Input field selects one of four audio inputs to the codec. Select EXT if the audio signal is coming from a microphone connected to the pink jack on J1 of the XSB-300E Board. Select LINE if the audio signal is arriving through the blue jack of J1. In general, INTO or INT1 should not be used unless you have a source of audio wired to the appropriate pins of the JP1 header.

The PM0, PM1, PM2 checkboxes control the power that goes to the input amplifier, ADC and DAC blocks of the AK4565, respectively. In general, these checkboxes should all be checked so these blocks receive power. The PM3 checkbox activates an analog loopback mode in the codec and should usually be left unchecked.

The De-emphasis field selects whether a filter is inserted into the audio input signal path to attenuate higher frequencies. This field should usually be set to OFF so that the codec operates with a flat input frequency response.

The Serial Format field selects the bit ordering and timing for the serial streams that come from and go to the codec ADC and DAC, respectively. The 20M/16L setting programs the codec to output 20 bits from the ADC starting with the most-significant bit in the first time slot of a 32-slot frame while 16 bits are sent to the DAC with the least-significant bit occupying the last slot of the frame. The 20M/20L is similar except that the DAC receives 20 bits instead of 16. Finally, the 20M/20M setting programs the codec to output 20 bits from the ADC starting with the most-significant bit in the first time slot of a 32-slot frame while 20 bits are sent to the DAC with the most-significant bit also occupying the first slot of the frame. The 20M/20M setting must be used if you want to apply an audio source and listen to it using the loopback feature of GXSSETCODEC.

The Sampling Freq. Field selects whether the codec operates at 32 or 48 Ksamples/second. This field should be set to 48 KHz if you are using the loopback feature of GXSSETCODEC.

The LTM, WTM, ZTM, FDTM, LMTH, RATT, FDAT, LMAT and REF fields all exert control over the automatic level control circuitry of the programmable gain amplifier on the input to the ADC. These settings are not critical to the basic operation of the codec. You should read the datasheet for the AK4565 to determine the exact effects of these settings.

The IPGA field selects the gain for the amplifier on the input to the ADC in the codec. This allows you to amplify low-level signals to make the best use of the signal range afforded by the ADC. The gain is automatically increased by an additional 22 dB if the Input field is set to EXT since this usually means a low-level signal from a microphone is the source of the audio input.

When checked, the ALC checkbox activates the automatic level control circuitry.

When checked, the FDIN and FDOUT checkboxes enable the circuitry that gradually increases and decreases the output from the DAC.

When checked, the FR checkbox allows the automatic level control to respond to impulse noise.

When not checked, the ZELMIN checkbox allows the automatic level control circuitry to change the input gain only on zero-crossings of the input signal.

1

2

3

4 5

6

7

8

9

10 11

12

13

14

15

16

17

18

30

40 41 42

43

44

45

46

47

48

49

50

51

52

53

54 55

56

57

58

59

60

61

62

# Listing 1: VHDL code for the default CPLD parallel port interface.

```

library ieee;

use ieee.std logic 1164.all;

use IEEE.std logic arith.all;

entity dwnldpar is

port(

-- parallel port data and status pins

std logic vector(7 downto 0);

pp_d:

in

std logic vector(5 downto 3);

pp s:

out

-- FPGA configuration pins

out std_logic_vector(0 downto 0); -- config. mode select (out)

fpga m:

std logic; -- active-low config. initiate (out)

fpga_program_n: out

fpga cclk:

out

std logic;

-- config. clock (out)

fpga cs n:

out std logic;

-- active-low chip-select (out)

fpga write n: out std logic;

-- active-low write-enable (out)

fpga init n: inout std logic;

-- config. initialization (in)

fpga done:

in std_logic;

-- config. done (in)

std_logic;

-- JTAG clock (out)

fpga_tck:

out

-- peripheral bus

pb d:

inout std_logic_vector(7 downto 0); -- config. data (out)

inout std logic vector(19 downto 0) -- address bus (in)

pb a:

);

end entity dwnldpar;

architecture arch of dwnldpar is

constant LO: std logic := '0';

constant HI: std_logic := '1';

constant HIZ: std_logic := 'Z';

constant SLAVE PARALLEL MODE: std logic vector(0 downto 0) := "0";

signal cclk: std logic;

signal config_data, nybble: std_logic_vector(3 downto 0);

signal cpld addr: std logic vector(3 downto 0);

begin

nybble

<= pp d(5 downto 2);

-- data from PC to board

cpld_addr <= fpga_init_n & pb_a(2 downto 0); -- selects CPLD profile</pre>

process(pp_d,pb_a,nybble,config_data,cclk,fpga_done,cpld_addr)

begin

<= HIZ;

fpga cs n

<= HIZ;

fpga write n

pb a

<= (others=>HIZ);

<= (others=>HIZ);

pb d

<= LO;

-- deactivate FPGA JTAG circuit

fpga_tck

fpga m

<= SLAVE PARALLEL MODE; -- set FPGA config mode</pre>

-- FPGA PROGRAM# comes from parallel port

fpga_program_n

\leq pp d(7);

cclk

\leq not pp d(0);

-- internal configuration clock

-- FPGA configuration clock

fpga_cclk

<= not cclk;

if fpga done=LO then-- FPGA is not configured

fpga_cs_n <= LO;</pre>

-- enable writing of config. data

fpga_write_n <= LO;</pre>

pb d

<= config data & nybble; -- two nybbles of config data</pre>

else -- FPGA is configured

fpga cs n \leq not pp d(1);

-- clock for data interchange

fpga_write_n <= pp_d(6);</pre>

-- reset for data interchange FSM

case conv integer (unsigned (cpld addr)) is

```

```

63

64

65

66

67

68

69

70

71

72

73

74

75

76

77

78

79

80

81

82

83

84

85

86

87

88

89

90

91

92

93

94

95

```

```

when 0 \Rightarrow -- I2C programming is selected by the FPGA

pb_d(0) <= not pp_d(1); -- I2C clock to SAA7114 & osc chips</pre>

<= pp d(6);

-- I2C data to SAA7114 & osc chips

pb d(1)

\leq pb_a(3);

-- I2C clock from SAA7114 & osc chips

pp_s(3)

pp s(4)

<= pb a(4);

-- I2C data from SAA7114 & osc chips

when 1 => -- stereo codec programming is selected by the FPGA

pb d(0) <= not pp d(1); -- config. clock to codec chip</pre>

pb_d(1)

<= pp d(6);

-- config. data to codec chip

pb_d(3)

\neq pp_d(5);

-- chip-select to codec chip

pp_s(4)

\neq pb_d(2);

-- config. data from codec chip

when 2 => -- data interchange interface

pb d(5 downto 2) <= pp d(5 downto 2); -- data nybble from PC to FPGA

pp s(5 downto 3) <= pb a(5 downto 3); -- data bits from FPGA to PC

when \overline{3} = -- GXSPORT/XSPORT interface

pb d(6 downto 0) <= pp_d(6 downto 0);</pre>

pp_s(5 downto 3) <= pb_a(5 downto 3);</pre>

when 4 \mid 5 \mid 6 \mid 7 \Rightarrow -- currently undefine CPLD modes

when others => -- CPLD is not selected by the FPGA

<= pb a(19); -- for reporting GXSTEST status</pre>

pp s(5)

end case;

end if;

end process;

-- gather 4-bit data from parallel port

process(cclk)

begin

if rising_edge(cclk) then

config data <= nybble;

end if;

end process;

end architecture arch;

```

## Listing 2: User-constraint file for the CPLD pin assignments.

```

# pin assignments for the XC9572XL CPLD chip on the XSB Board

# peripheral bus

net pb_d<0>

loc=p2;

# data bit D0 (in/out)

# data bit D1 (in/out)

net pb_d<1>

loc=p4;

net pb_d<2>

loc=p5;

# data bit D2 (in/out)

net pb_d<3>

loc=p6;

# data bit D3 (in/out)

# data bit D4 (in/out)

net pb d<4>

loc=p7;

net pb d<5>

loc=p8;

# data bit D5 (in/out)

# data bit D6 (in/out)

net pb d<6>

loc=p9;

net pb_d<7>

loc=p10; # data bit D7 (in/out)

net pb a<0>

loc=p1;

# address bit A0 (in/out)

net pb a<1>

loc=p64; # address bit A1 (in/out)

net pb a<2>

loc=p63; # address bit A2 (in/out)

net pb a<3>

loc=p62; # address bit A3 (in/out)

loc=p61; # address bit A4 (in/out)

net pb a<4>

net pb_a<5>

loc=p60; # address bit A5 (in/out)

loc=p50; # address bit A19 (in/out)

net pb_a<19>

# parallel port

net pp d<0>

loc=p33;

# data pin D0 (in)

net pp d<1>

loc=p32;

# data pin D1 (in)

net pp d<2>

loc=p31;

# data pin D2 (in)

net pp d<3>

loc=p27;

# data pin D3 (in)

loc=p25;

# data pin D4 (in)

net pp_d<4>

net pp_d<5>

loc=p24;

# data pin D5 (in)

net pp d<6>

loc=p23;

# data pin D6 (in)

loc=p22;

net pp d<7>

# data pin D7 (in)

net pp s < 3 >

loc=p34; # status pin S3 (out)

net pp s<4>

loc=p20; # status pin S4 (out)

net pp_s<5>

loc=p35; # status pin S5 (out)

# FPGA configuration interface

net fpga m<0>

loc=p36; # config. mode select (out)

net fpga_program_n loc=p39; # active-low config. initiate (out)

loc=p16; # config. clock (out)

net fpga cclk

net fpga cs n

loc=p15;

# active-low chip-select (out)

# active-low write-enable (out)

net fpga write n loc=p19;

net fpga init n loc=p38;

# config. initialization (in)

net fpga_done loc=p40; # config. done (in)

net fpga tck

loc=p13; # JTAG clock (out)

```

## Listing 3: VHDL code for the FPGA audio codec interface.

```

library ieee;

use ieee.std logic 1164.all;

use ieee.std_logic_arith.all;

use ieee.std logic unsigned.all;

entity cfgcodec is

port

fpga init n: out std logic;

-- INIT# pin

fpga clk: in std logic vector(1 downto 0);

pb d: in std logic vector(15 downto 0);

-- to parallel port data pin

pb_a: out std_logic_vector(19 downto 0);

-- to parallel port status pin

au csn n: out std logic;

-- audio codec chip-enable

au bclk: out std logic;

au mclk: out std logic;

au lrck: out std logic;

au sdti: out std logic;

au_sdto: in std_logic

);

end cfgcodec;

architecture arch of cfgcodec is

signal cnt: std logic vector(9 downto 0);

begin

fpga_init_n <= '0';</pre>

-- indicate that the codec is available for programming

pb_a(2 downto 0) <= "001";

-- parallel port codec configuration interface

au csn n \leq pb d(3);

process(fpga_clk(0))

begin

if (fpga clk(0) 'event and fpga clk(0) = '1') then

cnt <= cnt+1;

end if;

end process;

au_lrck <= cnt(9);</pre>

au bclk <= cnt(3);</pre>

au mclk <= cnt(1);

au sdti <= au sdto;

end arch;

```

## Listing 4: User-constraint file for the FPGA pin assignments.

```

\# pin assignments for the XC2S300E FPGA chip on the XSB Board

loc=p83;

net pb_a<0>

loc=p84;

net pb_a<1>

net pb_a<2>

loc=p86;

net fpga_init_n

loc=p107;

net pb_d<3>

loc=p135;

net au_csn_n

loc=p165;

net au bclk

loc=p166;

net au_mclk

loc=p167;

net au_lrck

loc=p168;

net au_sdti

loc=p169;

net au_sdto

loc=p173;

net fpga_clk<0>

loc=p182;

```