## **XSB-300E** Parallel Port Interface

October 20, 2003 (Version 1.0)

Application Note by D. Vanden Bout

### Summary

This application note describes the default parallel port interface circuit that is programmed into the XC9572XL CPLD on the XSB-300E Board. It also discusses how to change the parallel port interface to support other features.

### The Default Parallel Port Interface

Listing 1 shows the VHDL code for the default parallel port interface that is programmed into the XC9572XL CPLD on the XSB-300E Board. This interface provides two functions:

- It transfers configuration bitstreams from the PC to the SpartanIIE FPGA.

- It lets the PC and the SpartanIIE communicate through the parallel port after the FPGA is configured.

How the VHDL implements these functions is described below.

Lines 40 and 41 just give more meaningful names to some input signals.

The main functionality of the CPLD is defined by the process starting on line 43. It begins by setting the default values of some signals on lines 45–48. The JTAG circuitry of the SpartanIIE FPGA is kept quiescent so it cannot interfere by holding its clock pin low on line 49.

The circuitry that actually controls the configuration of the SpartanIIE device is described on lines 50–58. On line 50, the CPLD pulls down the M0 mode pin of the SpartanIIE device to set the FPGA into the Slave Parallel configuration mode (the M1 and M2 mode pins of the SpartanIIE are hard-wired on the XSB-300E PCB). The PROGRAM pin for the SpartanIIE is connected to data line D7 of the parallel port on line 51. A low level on D7 will initiate the configuration of the SpartanIIE and its DONE pin will go low. The low level on the DONE pin activates the functions described on lines 55–58. Low levels are placed on the chip-select and write-strobe of the SpartanIIE on lines 56 and 57, respectively. This enables the writing of byte-wide configuration data into the SpartanIIE. These pins are released after DONE goes high because they become general-purpose I/O pins after configuration is completed.

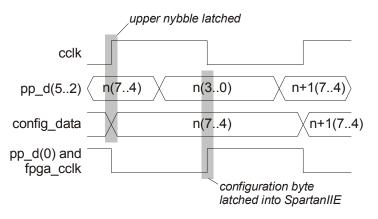

The configuration data bytes arrive as two four-bit nybbles over data lines D2–D5 (line 40). The upper nybble of each configuration byte is stored in the config\_data register on the rising edge of the cclk (lines 88–93). The inverse of parallel port data line D0 drives the internal cclk signal (line 52), so the data is latched into the config\_data register on the falling edge of D0.

The upper nybble in the config\_data register is concatenated with the lower nybble on the D2–D5 data lines to form a complete byte of configuration data (line 58). The configuration clock for the SpartanIIE is the inverse of the clock that controls the config\_data register (line 53). So the configuration data is latched into the SpartanIIE on the falling edge of cclk. The overall process of getting byte *n* of configuration data into the SpartanIIE looks like this:

Once all the configuration data enters the SpartanIIE, it will raise its DONE pin. This activates the circuitry described on lines 59–83 that allows the SpartanIIE to communicate with the PC parallel port through the CPLD. The chip-select and write-strobe of the SpartanIIE are used to receive a clock and reset signal from the PC to the FPGA (lines 60 and 61, respectively). These signals control state machines that are loaded into the SpartanIIE.

The FPGA outputs an address to ther CPLD to select one of the clauses in the case statement on lines 62– 82. As can be seen on line 41, the address is composed of the lower three bits of the peripheral address bus and the value on the INIT# pin of the FPGA (which becomes a general-purpose I/O pin after the FPGA is configured.)

If the CPLD address output by the FPGA is 0000, then the circuitry described by statements 63–67 is activated. This circuitry creates a pathway through the CPLD whereby the PC can send and receive the  $l^2C$  clock and data signals through the data and status pins of the parallel port to the FPGA. In this case, the FPGA must be configured to pass these signals onto the SCL and SDA signals that go to the  $l^2C$  peripherals on the XSB-300E Board (i.e., the programmable clock and the video decoder chips). This parallel port  $\rightarrow$ CPLD $\rightarrow$ FPGA pathway allows the XSTOOLs software utilities to program the oscillator frequency and the video decoder options.

If the CPLD address output by the FPGA is 0001, then the circuitry described by statements 68-72 is activated. This circuitry creates a pathway through the CPLD whereby the PC can send and receive the clock, data and chip-select signals through the data and status pins of the parallel port to the FPGA. The FPGA must be configured to pass these signals onto the CCLK, CDTI, CDTO and CSN# pins of the stereo codec on the XSB-300E Board. This parallel port→CPLD→FPGA pathway lets the XSTOOLs software utilities program the stereo codec options.

If the CPLD address output by the FPGA is 0010. then the circuitry described by statements 73-75 is activated. This circuitry creates a pathway through the CPLD whereby the PC can send and receive data through the data and status pins of the parallel port to the FPGA. The FPGA must be configured to assemble complete address and data fields from these signals (using a state machine driven by the clock from line 60) which it can then use to access various peripherals on the XSB-300E Board. This pathway used. for example. the is SO GXSLOAD/XSLOAD software utilities can upload/download the SRAM and SDRAM on the board.

If the CPLD address output by the FPGA is 0011, then the circuitry described by statements 76–78 is activated. This circuitry lets the PC force a value on the lower seven bits of the peripheral data bus using the data pins of the parallel port. The FPGA can operate upon this value and return a result through the parallel port status pins using three bits of the peripheral address bus. This pathway is used by the GXSPORT/XSPORT software utilities to apply test vectors to simple designs loaded into the FPGA and receive results.

The CPLD does not open a pathway between the parallel port and the rest of the XSB-300E Board when the CPLD address is 01XX (line 79). Addresses in this range can be used for new CPLD modes of operation.

If the FPGA places a high level on its INIT# pin, then the CPLD circuitry defined by lines 80–81 is activated. Bit A19 of the peripheral address bus is passed through the CPLD to a status pin of the parallel port while the rest of the parallel port remains isolated from the board. This circuitry is used solely to pass a status signal that reports the health of the XSB-300E Board back to the GXSTEST/XSTEST software utility running on the PC.

#### Changing the Parallel Port Interface

The parallel port interface is stored in the nonvolatile Flash of the XC9572XL CPLD on the XSB-300E Board. Any design you load into the CPLD will become active as soon as the XSB-300E Board powers up. So it is possible to load a faulty interface design into the CPLD that makes it impossible to program the SpartanIIE even after you cycle the power. The only solution is to explicitly reprogram the CPLD with a functional interface using GXSLOAD. Then the XSB-300E Board will function correctly again.

All you need to do when changing the parallel port interface is to add a new clause to the case statement on lines 62–83. Just select one of the unused CPLD addresses and add the VHDL code for your additional circuitry there.

When generating a new interface for the CPLD, you must set the USERCODE signature register to the four-character string <4>!. The XSTOOLs utilities look for this signature in the CPLD to verify that a valid interface is present.

Listing 1: VHDL code for the default CPLD parallel port interface.

```

library ieee;

use ieee.std logic 1164.all;

use IEEE.std logic arith.all;

entity dwnldpar is

port(

-- parallel port data and status pins

std_logic_vector(7 downto 0);

pp_d:

in

std logic vector (5 downto 3);

pp s:

out

-- FPGA configuration pins

out std_logic_vector(0 downto 0); -- config. mode select (out)

fpga m:

std logic;

-- active-low config. initiate (out)

fpga_program_n: out

fpga cclk:

std logic;

-- config. clock (out)

out

fpga cs n:

out std logic;

-- active-low chip-select (out)

fpga write n: out std logic;

-- active-low write-enable (out)

fpga init n: inout std logic;

-- config. initialization (in)

fpga done:

in std logic;

-- config. done (in)

std_logic;

-- JTAG clock (out)

fpga_tck:

out

-- peripheral bus

pb d:

inout std_logic_vector(7 downto 0); -- config. data (out)

inout std logic vector(19 downto 0) -- address bus (in)

pb a:

);

end entity dwnldpar;

architecture arch of dwnldpar is

constant LO: std logic := '0';

constant HI: std_logic := '1';

constant HIZ: std logic := 'Z';

constant SLAVE PARALLEL MODE: std logic vector(0 downto 0) := "0";

signal cclk: std logic;

signal config_data, nybble: std_logic_vector(3 downto 0);

signal cpld addr: std logic vector(3 downto 0);

begin

nybble

<= pp d(5 downto 2);

-- data from PC to board

cpld_addr <= fpga_init_n & pb_a(2 downto 0); -- selects CPLD profile

process(pp_d,pb_a,nybble,config_data,cclk,fpga_done,cpld_addr)

begin

<= HIZ;

fpga cs n

fpga write n

<= HIZ;

pb a

<= (others=>HIZ);

<= (others=>HIZ);

pb d

<= LO;

-- deactivate FPGA JTAG circuit

fpga_tck

fpga m

<= SLAVE PARALLEL MODE; -- set FPGA config mode

-- FPGA PROGRAM# comes from parallel port

fpga_program_n

<= pp d(7);

cclk

<= not pp d(0);

-- internal configuration clock

-- FPGA configuration clock

fpga_cclk

<= not cclk;

if fpga done=LO then-- FPGA is not configured

fpga_cs_n <= LO;

-- enable writing of config. data

fpga_write_n <= LO;</pre>

pb d

<= config data & nybble; -- two nybbles of config data

else -- FPGA is configured

fpga cs n <= not pp d(1);</pre>

-- clock for data interchange

fpga_write_n <= pp_d(6);</pre>

-- reset for data interchange FSM

case conv integer(unsigned(cpld addr)) is

```

61

62

1

2

| <pre>when 0 =&gt; I2C programming is selected by the FPGA</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre>pb_d(0) &lt;= not pp_d(1); I2C clock to SAA7114 &amp; osc chips<br/>pb_d(1) &lt;= pp_d(6); I2C clock from SAA7114 &amp; osc chips<br/>pp_s(3) &lt;= pb_a(3); I2C clock from SAA7114 &amp; osc chips<br/>pp_s(4) &lt;= pb_a(4); I2C clock from SAA7114 &amp; osc chips<br/>when 1 =&gt; stereo codec programming is selected by the FPGA<br/>pb_d(0) &lt;= not pp_d(1); config. clock to codec chip<br/>pb_d(1) &lt;= pp_d(6); config. data to codec chip<br/>pb_d(3) &lt;= pp_d(5); chip-select to codec chip<br/>when 2 =&gt; data interchange interface<br/>pb_d(5 downto 2) &lt;= pp_d(5 downto 2); data nybble from PC to FPGA<br/>pp_s(5 downto 3) &lt;= pb_d(5 downto 3); data bits from FPGA to PC<br/>when 3 =&gt; GXSPORT/XSPORT interface<br/>pb_d(6 downto 0) &lt;= pp_d(6 downto 0);<br/>pp_s(5 downto 3) &lt;= pb_a(5 downto 3);<br/>when 4   5   6   7 =&gt; currently undefine CPLD modes<br/>when others =&gt; CPLD is not selected by the FPGA<br/>pp_s(5) &lt;= pb_a(19); for reporting GXSTEST status<br/>end case;<br/>end if;<br/>end process;<br/> gather 4-bit data from parallel port<br/>process(cclk)<br/>begin<br/>if rising_edge(cclk) then<br/>config_data &lt;= nybble;<br/>end if;<br/>end process;</pre> | 3        | when $0 \implies$ I2C programming is selected by the FPGA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| <pre>pb_d(1) &lt;= pp_d(6); I2C data to SAA7114 &amp; osc chips<br/>pp_s(3) &lt;= pb_a(3); I2C data from SAA7114 &amp; osc chips<br/>pp_s(4) &lt;= pb_a(4); I2C data from SAA7114 &amp; osc chips<br/>when 1 =&gt; stereo codec programming is selected by the FPGA<br/>pb_d(0) &lt;= not pp_d(1); config. clock to codec chip<br/>pb_d(1) &lt;= pp_d(6); chip-select to codec chip<br/>pb_d(3) &lt;= pp_d(5); chip-select to codec chip<br/>when 2 =&gt; data interchange interface<br/>pb_d(5 downto 2) &lt;= pp_d(5 downto 2); data nybble from PC to FPGA<br/>pp_s(5 downto 3) &lt;= pp_d(6 downto 0);<br/>pp_s(5 downto 0) &lt;= pp_d(6 downto 0);<br/>pp_s(5 downto 3) &lt;= pb_a(5 downto 3);<br/>when 4   5   6   7 =&gt; currently undefine CPLD modes<br/>when others =&gt; CPLD is not selected by the FPGA<br/>pp_s(5) &lt;= pb_a(19); for reporting GXSTEST status<br/>end case;<br/>end if;<br/>end process;<br/> gather 4-bit data from parallel port<br/>process;<br/>end if;<br/>end process;</pre>                                                                                                                                                                                                                          | 1        | $ph d(0) \leq not pp d(1)$ : I2C clock to SAA7114 & osc chips                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| <pre>when 1 =&gt; stereo codec programming is selected by the FPGA</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 5        | $p_{\mu_{n}}(z) = p_{\mu_{n}}(z)$ = $p_{\mu_{n}}(z)$ = $p_{\mu_{$ |

| <pre>when 1 =&gt; stereo codec programming is selected by the FPGA</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Ś        | $p_{1}$ $(1)$ $(-p_{1})$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$ $(2)$                                                                                                                                                                                                                                                   |

| <pre>when 1 =&gt; stereo codec programming is selected by the FPGA</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 7        | $pp_{-}(3) < -pb_{-}(3), - 120  clock from sparsing we can be set of the state o$                                                                                                                                                                                                                                                     |

| <pre>pb_d(0) &lt;= not pp_d(1); config. clock to codec chip<br/>pb_d(1) &lt;= pp_d(6); config. data to codec chip<br/>pb_d(3) &lt;= pp_d(5); config. data from codec chip<br/>pp_s(4) &lt;= pb_d(2); config. data from codec chip<br/>when 2 =&gt; data interchange interface<br/>pb_d(5 downto 2) &lt;= pp_d(5 downto 2); data nybble from PC to FPGA<br/>pp_s(5 downto 3) &lt;= pb_a(5 downto 3); data bits from FPGA to PC<br/>when 3 =&gt; GXSPORT/XSPORT interface<br/>pb_d(6 downto 0) &lt;= pp_d(6 downto 0);<br/>pp_s(5 downto 3) &lt;= pb_a(5 downto 3);<br/>when 4   5   6   7 =&gt; currently undefine CPLD modes<br/>when others =&gt; CPLD is not selected by the FPGA<br/>pp_s(5) &lt;= pb_a(19); for reporting GXSTEST status<br/>end case;<br/>end if;<br/>end process;<br/> gather 4-bit data from parallel port<br/>process(cclk)<br/>begin<br/>if rising_edge(cclk) then<br/>config_data &lt;= nybble;<br/>end if;<br/>end process;</pre>                                                                                                                                                                                                                                                                                  | <u></u>  | pp_s(4) <= pb_a(4); 12C data from SAA/114 & osc chips                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| <pre>pb_d(1) &lt;= pp_d(6); config. data to codec chip<br/>pb_d(3) &lt;= pp_d(5); chip-select to codec chip<br/>pp_s(4) &lt;= pb_d(2); config. data from codec chip<br/>when 2 =&gt; data interchange interface<br/>pb_d(5 downto 2) &lt;= pp_d(5 downto 2); data nybble from PC to FPGA<br/>pp_s(5 downto 3) &lt;= pb_a(5 downto 3); data bits from FPGA to PC<br/>when 3 =&gt; GXSPORT/XSPORT interface<br/>pb_d(6 downto 0) &lt;= pp_d(6 downto 0);<br/>pp_s(5 downto 3) &lt;= pb_a(5 downto 3);<br/>when 4   5   6   7 =&gt; currently undefine CPLD modes<br/>when others =&gt; CPLD is not selected by the FPGA<br/>pp_s(5) &lt;= pb_a(19); for reporting GXSTEST status<br/>end case;<br/>end if;<br/>end process;<br/> gather 4-bit data from parallel port<br/>process(cclk)<br/>begin<br/>if rising_edge(cclk) then<br/>config_data &lt;= nybble;<br/>end if;<br/>end process;</pre>                                                                                                                                                                                                                                                                                                                                                | 5        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| <pre>pb_d(3) &lt;= pp_d(5); chip-select to codec chip<br/>pp_s(4) &lt;= pb_d(2); config. data from codec chip<br/>when 2 =&gt; data interchange interface<br/>pb_d(5 downto 2) &lt;= pp_d(5 downto 2); data nybble from PC to FPGA<br/>pp_s(5 downto 3) &lt;= pb_a(5 downto 3); data bits from FPGA to PC<br/>when 3 =&gt; GXSPORT/XSPORT interface<br/>pb_d(6 downto 0) &lt;= pp_d(6 downto 0);<br/>pp_s(5 downto 3) &lt;= pb_a(5 downto 3);<br/>when 4   5   6   7 =&gt; currently undefine CPLD modes<br/>when others =&gt; CPLD is not selected by the FPGA<br/>pp_s(5) &lt;= pb_a(19); for reporting GXSTEST status<br/>end case;<br/>end if;<br/>end process;<br/> gather 4-bit data from parallel port<br/>process(cclk)<br/>begin<br/>if rising_edge(cclk) then<br/>config_data &lt;= nybble;<br/>end if;<br/>end process;</pre>                                                                                                                                                                                                                                                                                                                                                                                                      | 1        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| <pre>when 2 =&gt; data interchange interface<br/>pb_d(5 downto 2) &lt;= pp_d(5 downto 2); data nybble from PC to FPGA<br/>pp_s(5 downto 3) &lt;= pb_a(5 downto 2); data bits from FPGA to PC<br/>when 3 =&gt; GXSPORT/XSPORT interface<br/>pb_d(6 downto 0) &lt;= pp_d(6 downto 0);<br/>pp_s(5 downto 3) &lt;= pb_a(5 downto 3);<br/>when 4   5   6   7 =&gt; currently undefine CPLD modes<br/>when others =&gt; CPLD is not selected by the FPGA<br/>pp_s(5) &lt;= pb_a(19); for reporting GXSTEST status<br/>end case;<br/>end if;<br/>end process;<br/> gather 4-bit data from parallel port<br/>process(cclk)<br/>begin<br/>if rising_edge(cclk) then<br/>config_data &lt;= nybble;<br/>end if;<br/>end process;<br/></pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | )        | pb_d(1) <= pp_d(6); config. data to codec chip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| <pre>when 2 =&gt; data interchange interface<br/>pb_d(5 downto 2) &lt;= pp_d(5 downto 2); data nybble from PC to FPGA<br/>pp_s(5 downto 3) &lt;= pb_a(5 downto 2); data bits from FPGA to PC<br/>when 3 =&gt; GXSPORT/XSPORT interface<br/>pb_d(6 downto 0) &lt;= pp_d(6 downto 0);<br/>pp_s(5 downto 3) &lt;= pb_a(5 downto 3);<br/>when 4   5   6   7 =&gt; currently undefine CPLD modes<br/>when others =&gt; CPLD is not selected by the FPGA<br/>pp_s(5) &lt;= pb_a(19); for reporting GXSTEST status<br/>end case;<br/>end if;<br/>end process;<br/> gather 4-bit data from parallel port<br/>process(cclk)<br/>begin<br/>if rising_edge(cclk) then<br/>config_data &lt;= nybble;<br/>end if;<br/>end process;<br/></pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1        | pb_d(3) <= pp_d(5); chip-select to codec chip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| <pre>when 2 =&gt; data interchange interface<br/>pb_d(5 downto 2) &lt;= pp_d(5 downto 2); data nybble from PC to FPGA<br/>pp_s(5 downto 3) &lt;= pb_a(5 downto 2); data bits from FPGA to PC<br/>when 3 =&gt; GXSPORT/XSPORT interface<br/>pb_d(6 downto 0) &lt;= pp_d(6 downto 0);<br/>pp_s(5 downto 3) &lt;= pb_a(5 downto 3);<br/>when 4   5   6   7 =&gt; currently undefine CPLD modes<br/>when others =&gt; CPLD is not selected by the FPGA<br/>pp_s(5) &lt;= pb_a(19); for reporting GXSTEST status<br/>end case;<br/>end if;<br/>end process;<br/> gather 4-bit data from parallel port<br/>process(cclk)<br/>begin<br/>if rising_edge(cclk) then<br/>config_data &lt;= nybble;<br/>end if;<br/>end process;<br/></pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2        | pp s(4) <= pb d(2); config. data from codec chip                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| <pre>pb_d(5 downto 2) &lt;= pp_d(5 downto 2); data nybble from PC to FPGA</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 3        | when $2 \implies$ data interchange interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| <pre>pp_s(5 downto 3) &lt;= pb_a(5 downto 3); data bits from FPGA to PC<br/>when 3 =&gt; GXSPORT/XSPORT interface<br/>pb_d(6 downto 0) &lt;= pp_d(6 downto 0);<br/>pp_s(5 downto 3) &lt;= pb_a(5 downto 3);<br/>when 4   5   6   7 =&gt; currently undefine CPLD modes<br/>when others =&gt; CPLD is not selected by the FPGA<br/>pp_s(5) &lt;= pb_a(19); for reporting GXSTEST status<br/>end case;<br/>end if;<br/>end process;<br/> gather 4-bit data from parallel port<br/>process(cclk)<br/>begin<br/>if rising_edge(cclk) then<br/>config_data &lt;= nybble;<br/>end if;<br/>end process;</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| <pre>when 3 =&gt; GXSPORT/XSPORT interface<br/>pb_d(6 downto 0) &lt;= pp_d(6 downto 0);<br/>pp_s(5 downto 3) &lt;= pb_a(5 downto 3);<br/>when 4   5   6   7 =&gt; currently undefine CPLD modes<br/>when others =&gt; CPLD is not selected by the FPGA<br/>pp_s(5) &lt;= pb_a(19); for reporting GXSTEST status<br/>end case;<br/>end if;<br/>end process;<br/> gather 4-bit data from parallel port<br/>process(cclk)<br/>begin<br/>if rising_edge(cclk) then<br/>config_data &lt;= nybble;<br/>end if;<br/>end process;</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| <pre>pb_d(6 downto 0) &lt;= pp_d(6 downto 0);<br/>pp_s(5 downto 3) &lt;= pb_a(5 downto 3);<br/>when 4   5   6   7 =&gt; currently undefine CPLD modes<br/>when others =&gt; CPLD is not selected by the FPGA<br/>pp_s(5) &lt;= pb_a(19); for reporting GXSTEST status<br/>end case;<br/>end if;<br/>end process;<br/> gather 4-bit data from parallel port<br/>process(cclk)<br/>begin<br/>if rising_edge(cclk) then<br/>config_data &lt;= nybble;<br/>end if;<br/>end process;</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 5        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| <pre>pp_s(5 downto 3) &lt;= pb_a(5 downto 3);<br/>when 4   5   6   7 =&gt; currently undefine CPLD modes<br/>when others =&gt; CPLD is not selected by the FPGA<br/>pp_s(5) &lt;= pb_a(19); for reporting GXSTEST status<br/>end case;<br/>end if;<br/>end process;<br/> gather 4-bit data from parallel port<br/>process(cclk)<br/>begin<br/>if rising_edge(cclk) then<br/>config_data &lt;= nybble;<br/>end if;<br/>end process;</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 7        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| <pre>when 4   5   6   7 =&gt; currently undefine CPLD modes<br/>when others =&gt; CPLD is not selected by the FPGA</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 2        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| <pre>when others =&gt; CPLD is not selected by the FPGA</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | á        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |