# Parallel Cable III Emulator for the XSB-300E Board

October 4, 2003 (Version 1.0)

Application Note by D. Vanden Bout

### **Summary**

This application note shows how to configure the XC9572XL CPLD on the XSB-300E Board so its parallel port interface emulates the functions of the Xilinx Parallel Cable III. This lets you use the Xilinx WebPACK JTAG tools with the XSB-300E Board through its simple 25-wire downloading cable.

# Why Emulate the Parallel Cable III?

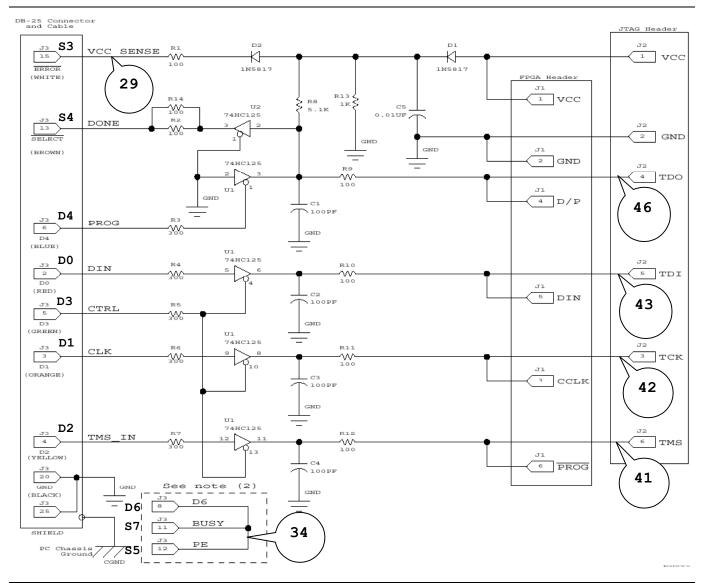

Xilinx WebPACK software contains tools for downloading and testing SpartanIIE FPGAs through their their JTAG interface. One of the ways these tools access the FPGA is through a Parallel Cable III connected from the FPGA to the parallel port of a PC. A schematic for the Parallel Cable III (henceforth referred to as PCBLIII) is shown in Figure 1.

The SpartanIIE FPGA on the XSB-300E Board is accessed from the PC parallel port through a simple 25-wire cable that connects to an XC9572XL CPLD on the XSB-300E Board. The CPLD can be programmed to pass signals from the parallel port to and from the JTAG pins of the SpartanIIE device. The XSB-300E Board is supplied with a default CPLD configuration that lets you download bitstreams to the SpartanIIE using the GXSLOAD utility provided by XESS.

This application note describes an alternate circuit that allows the CPLD to emulate the JTAG functions of the PCBLIII. By loading this circuit into the CPLD, you can use all the Xilinx downloading and testing tools with the XSB-300E Board through the simple downloading cable provided by XESS.

#### VHDL for the Parallel Cable III Emulator

Listing 1 shows the VHDL code for the PCBLIII emulator that is programmed into the XC9572XL CPLD on the XSB-300E Board. This interface provides two functions:

It transfers configuration bitstreams from the PC to the SpartanIIE FPGA using the JTAG interface.  After the SpartanIIE FPGA is configured and its DONE pin goes high, the JTAG interface is used to readback and/or test the FPGA.

How the VHDL implements these functions is described below.

Line 29 outputs a high logic level to status pin S3 of the parallel port. The Xilinx software checks for a high level on this status pin which indicates that power is being supplied to the PCBLIII.

The Xilinx software also checks for the presence of the PCBLIII by looping a signal from parallel port data pin D6 back through two of the status pins S5 and S7. Line 34 handles the loop from D6 back to S5. The CPLD cannot pass D6 to S7, however, because its TDO pin is already attached to S7. Therefore, the shunt on jumper JP1 has to be moved to the xi position to manually connect D6 and S7.

Line 36 drives the mode pins of the SpartanIIE FPGA to set it in the slave-serial configuration mode. This doesn't really do anything since the SpartanIIE will be programmed through its JTAG interface. Line 37 holds the /PROGRAM pin of the SpartanIIE at a high logic level to prevent accidental erasure of the FPGA configuration.

Lines 41-43 connect parallel port data pins D2, D1, and D0 to the SpartanIIE TMS, TCK, and TDI JTAG pins if D3 is low. The TMS, TCK and TDI inputs are allowed to float when D3 is high.

Line 46 passes the FPGA JTAG TDO signal back to the PC through status pin S4 of the paralle port. S4 is driven low when data pin D4 is low.

The PCBLIII emulator I/O pin assignments for the CPLD on the XSB-300E Board are shown in Listing 2.

## Using the Parallel Cable III Emulator

First, connect the XSB-300E Board to the parallel port of a PC through the simple 25-wire cable provided by XESS. Make sure the shunt on jumper JP1 is in the **xs** position. Then download the piiijtag.svf file into the XC9572XL CPLD using the GXSLOAD tool from XESS. Now move the shunt on JP1 to the **xi** position. At this point, the bitstream downloading portion of the PCBLIII emulator is active.

Next, double-click the Configure Device (iMPACT) icon in the Process pane of the WebPACK **Project Navigator** window. (This discussion assumes you already have a SpartanIIE design synthesized and implemented in WebPACK 5.2.).

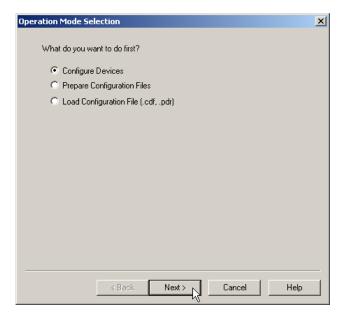

In the **Operation Mode Selection** window, select the Configure Devices option since we are going to configure the FPGA on the XSB-300E Board (i.e., download a bitstream file to it). Then click on the Next button.

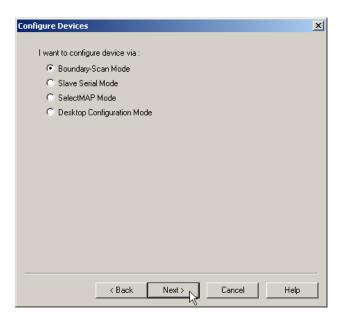

Now the **Configure Devices** window appears. Previously, we programmed the CPLD on the XSB-300E Board so it would support programming of the FPGA through its boundary-scan (i.e. JTAG) pins. So select the Boundary-Scan Mode option and click on the Next button.

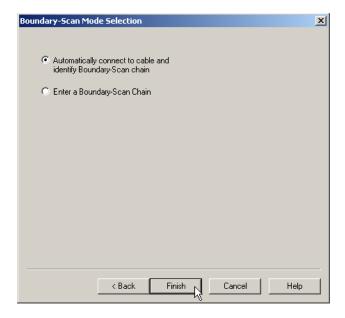

Boundary-scan mode allows the configuration of multiple FPGAs connected together in a chain. To do this, the iMPACT software needs to know the types of the FPGAs in the chain. We know there is just a single FPGA on the XSB-300E Board and we could easily describe this to iMPACT. But iMPACT can also probe the boundary-scan chain and automatically identify the types of the FPGAs. This is even easier, so we select the automatic identification option and click on the Finish button.

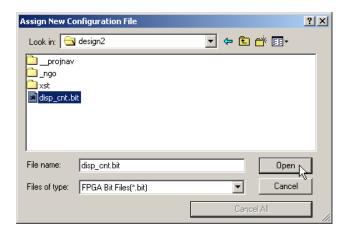

The iMPACT software will probe the boundary-scan chain and find there is a single FPGA in it. Now we need to tell iMPACT what bitstream file we want to download into this FPGA. Click on the OK button to proceed.

The Assign New Configuration File window now appears. Go to the folder where the bitstream file is located and highlight it. Then click on the Open button.

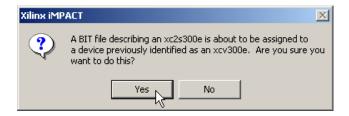

Now iMPACT may warn us that the bitstream file we selected is for an XC2S300E FPGA but it detected an XCV300E FPGA in the boundary-scan chain. The XC2S300E FPGA was developed as a low-cost variant of the XCV300E FPGA and they both share the same boundary-scan identification code. We know the XSB-300E Board has an XC2S300E FPGA that is compatible with the bitstream file, so we can click on the Yes button and move on.

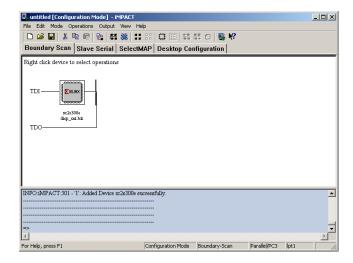

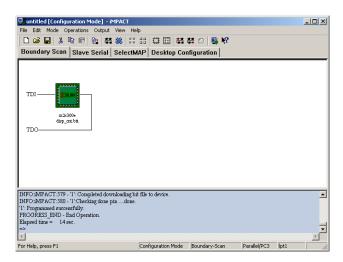

Now the main **iMPACT** window shows a boundary-scan chain consisting of a single XC2S300E FPGA.

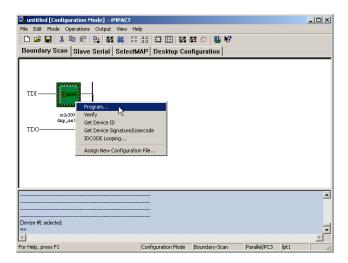

Now right-click on the xc2s300e icon and select the Program... item on the pop-up menu.

The **Program Options** window will appear. All we need to do at this point is click on the OK button to begin loading the bitstream file into the FPGA.

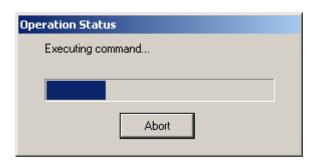

The progress of the bitstream download will be displayed. The download operation should complete within twenty seconds.

After the download operation completes, we can check the status messages in the bottom pane of the **iMPACT** window to see the FPGA was configured successfully.

Figure 1: Xilinx Parallel Cable III schematic. The line numbers of the VHDL code in Listing 1 associated with each schematic element are shown.

1

2

3

5

6

7

8

9 10

11

12

13

14

15

16

17

18

46

47 48

#### Listing 1: VHDL code for the Parallel Cable III emulator.

```

library ieee;

use ieee.std logic 1164.all;

entity piiijtag is

port(

-- parallel port data and status pins

ppd:

in std_logic_vector(6 downto 0);

out std logic vector(5 downto 3);

-- Spartan2E FPGA pins

S2 tck:

out std logic; -- driver to Spartan2E JTAG clock

S2 tms:

out std logic; -- driver to Spartan2E JTAG mode input

out std logic; -- driver to Spartan2E JTAG serial data input

S2 tdi:

S2 tdo:

in std logic; -- input from Spartan2E JTAG serial data output

S2 prog n: out std logic; -- driver to Spartan2E /PROGRAM pin

out std logic vector(0 downto 0) -- Spartan2E config mode pins

);

end piiijtag;

architecture arch of piiijtag is

constant NO: std_logic := '0';

constant YES: std_logic := '1';

constant LO: std_logic := '0';

constant HI: std_logic := '1';

constant SLAVE SERIAL MODE: std logic vector(0 downto 0) := "1";

-- the XSB power status is sent back through the parallel port status pin 3

<= HI; -- tell the PC that the VCC for the XSB board is OK

-- the cable is detected by sending data through data pin 6 and returning

-- it on status pins 5 and 7. Status pin 7 is used by the JTAG TDO

-- pin of the XC9500XL CPLD on the XSB Board, so place a shunt at position "xi"

-- of jumper JP1 to make this connection.

pps(5)

<= ppd(6);

S2 m

<= SLAVE SERIAL MODE; -- set Spartan2E config mode pins

-- prevent any accidental reconfiguration

S2 prog n <= HI;

-- drive the Spartan2E JTAG pins from the parallel port when tristate

-- control pin (parallel port data pin 3) is low.

S2 tms

<= ppd(2) when ppd(3)=LO else 'Z';

S2 tck

<= ppd(1) when ppd(3)=LO else 'Z';

S2 tdi

\leq ppd(0) when ppd(3)=LO else 'Z';

-- the JTAG TDO output is sent back through the status pin

<= S2 tdo when ppd(4)=HI else LO;

end arch;

```

#### Listing 2: User-constraint file for CPLD pin assignments.

```

1

2

# pin assignments for the XC9572XL CPLD chip on the XSA Board

3

4

5

# Spartan2 FPGA connections to CPLD

6

# net S2 clk

loc=p42;

7

net S2_tck

loc=p13;

8

# net \overline{S2} dout loc=p18;

9

net S2 tms

loc=p18;

10

# net S2 din

loc=p2;

11

# net S2 wr n loc=p19;

12

net S2 tdo

loc=p19;

13

# net S2_cs_n loc=p15;

14

net S2 tdi

loc=p15;

15

# net S2 init n

loc=p38;

16

# net S2 done loc=p40;

17

net S2 prog n loc=p39;

18

# net S2 cclk

loc=p16;

19

net S2_m<0>

loc=p36;

20

21

# net S2_d<0>

loc=p2;

# net S2_d<1>

loc=p4;

# net S2_d<2>

# net S2_d<3>

# net S2_d<4>

22

loc=p5;

23

loc=p6;

24

loc=p7;

25

# net S2 d<5>

loc=p8;

26

# net S2 d<6>

loc=p9;

27

# net S2 d<7>

loc=p10;

28

# net S2 a<0>

loc=p1;

29

# net S2 a<1>

loc=p64;

30

# net S2 a<2>

loc=p63;

31

# net S2 a<3>

loc=p62;

32

# net S2 a<4>

loc=p61;

33

# net S2_a<5>

loc=p60;

34

# net S2_a<6>

loc=p59;

35

# net S2_a<7>

loc=p58;

# net S2_a<8>

# net S2_a<9>

# net S2_a<10>

# net S2_a<11>

36

loc=p45;

37

loc=p44;

38

loc=p57;

39

loc=p43;

40

# net S2 a<12>

loc=p56;

41

# net S2_a<13>

loc=p46;

42

# net S2 a<14>

loc=p47;

43

# net S2 a<15>

loc=p52;

44

# net S2 a<16>

loc=p51;

45

# net S2 a<17>

loc=p48;

46

# net S2 rst n

loc=p50;# Flash reset

47

# net S2_oe_n loc=p12;# Flash output-enable

48

# net S2_we_n loc=p49;# Flash write-enable

49

# net S2_ce_n

loc=p11;# Flash chip-enable

50

51

# Flash RAM

52

# net fd<0>

loc=p2;

53

# net fd<1>

loc=p4;

54

# net fd<2>

loc=p5;

55

# net fd<3>

loc=p6;

56

# net fd<4>

loc=p7;

57

# net fd<5>

loc=p8;

58

# net fd<6>

loc=p9;

59

# net fd<7>

loc=p10;

60

# net fa<0>

loc=p1;

61

# net fa<1>

loc=p64;

62

# net fa<2>

loc=p63;

```

```

63

# net fa<3>

loc=p62;

64

loc=p61;

# net fa<4>

65

# net fa<5>

loc=p60;

66

# net fa<6>

loc=p59;

67

# net fa<7>

loc=p58;

68

loc=p45;

# net fa<8>

69

loc=p44;

# net fa<9>

70

# net fa<10>

loc=p57;

71

# net fa<11>

loc=p43;

72

loc=p56;

# net fa<12>

73

# net fa<13>

loc=p46;

74

# net fa<14>

loc=p47;

75

# net fa<15>

loc=p52;

76

# net fa<16>

loc=p51;

77

# net fa<17>

loc=p48;

78

loc=p50;# Flash reset

# net frst_n

79

# net foe n

loc=p12;# Flash output-enable

80

# net fwe n

loc=p49; # Flash write-enable

81

# net fce n

loc=p11;# Flash chip-enable

82

83

# DIP and pushbutton switches

84

loc=p47;

# net dipsw<1>

85

# net dipsw<2>

loc=p52;

86

# net dipsw<3>

loc=p51;

87

# net dipsw<4>

loc=p48;

88

89

# 7-segment LEDs

90

loc=p10;

# net s<0>

loc=p2;

91

# net s<1>

92

# net s<2>

loc=p9;

93

# net s<3>

loc=p8;

94

# net s<4>

loc=p5;

95

# net s<5>

loc=p7;

96

# net s<6>

loc=p6;

97

# net dp loc=p4;

98

99

# programmable oscillator

100

# net clk

loc=p17;

101

102

# parallel port

103

net ppd<0>

loc=p33;

104

loc=p32;

net ppd<1>

105

net ppd<2>

loc=p31;

loc=p27;

106

net ppd<3>

107

net ppd<4>

loc=p25;

108

# net ppd<5>

loc=p24;

109

net ppd<6>

loc=p23;

110

# net ppd<7>

loc=p22;

111

net pps<3>

loc=p34;

112

net pps<4>

loc=p20;

113

net pps<5>

loc=p35;

114

```